一个FPGA生态,打通多种高速视频接口

PolarFire® FPGA助力4K / 8K机器视觉快速落地 如果您正在做高速成像或机器视觉系统开发,那么好消息来了——只用一套PolarFire FPGA生态,就能同时搞定SDI、SLVS-EC 和 CoaXPress™接口! PolarFire FPGA 通过统一的平台,大幅简化设计流程,让复杂的视频接口开发变得更高效、更可控。 三种方式,全面加速您的下一代设计 SDI Rx/Tx I

纳米网嵌入式开发频道 — 提供嵌入式开发领域最新资讯、技术文章和行业动态。

PolarFire® FPGA助力4K / 8K机器视觉快速落地 如果您正在做高速成像或机器视觉系统开发,那么好消息来了——只用一套PolarFire FPGA生态,就能同时搞定SDI、SLVS-EC 和 CoaXPress™接口! PolarFire FPGA 通过统一的平台,大幅简化设计流程,让复杂的视频接口开发变得更高效、更可控。 三种方式,全面加速您的下一代设计 SDI Rx/Tx I

工程名称:60多元手搓摩托车 BSD 盲区监测! 工程作者:zaodianshane 前言 我希望做一个雷达。 在骑行的时候,只要有车/人靠近盲区。 雷达就会亮灯提醒我。 本文主要分享这个雷达的开源方案! 但在分享之前,俺想先说明一下 *其实我并不是专业做嵌入式这块的,我是做建筑工程管理这块工作的。可以说是一个完全零基础的小白。*我都是近1个月利用晚上下班时间看视频学习画板子做电路测试,看人家的

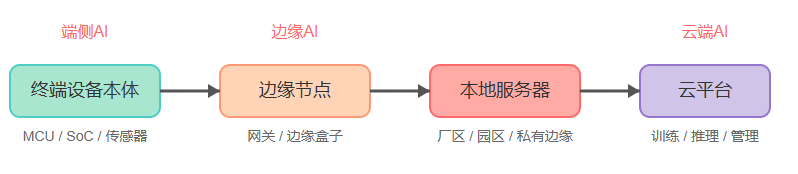

文章简介 这几个词现在被混着用得非常厉害。很多时候,一篇文章里前面写“边缘AI”,后面又说“端侧AI”,再往后又说“AI+嵌入式”,读下来感觉都差不多,但其实它们说的不是同一个维度。 更麻烦的是,很多真实项目同时跨了多个概念。你如果只记定义,不看实际例子,还是很容易分不清。 所以这篇增强版不只讲概念,还会把每个词放进真实工程场景里去解释。你看完之后,至少能知道:一个词到底是在说“行业融合”、还是在

工程名称:提醒喝水杯垫V2.0 工程作者:平韵の立创小分部 前言 这,是一个提醒喝水杯垫~ DIY成本仅80! 诶?这时候可能就有人说了 做一个不如买一个! 的确是这样的。 但,如果你了解到了它的这些功能,或许你会有不一样的看法…… *0***1 它有什么功能? ” 它会提醒你喝水:当你放下水杯,杯垫就会开始倒计时,时间到会提醒你喝水 可自定义倒计时时间 屏幕实时显示:时间,天气,

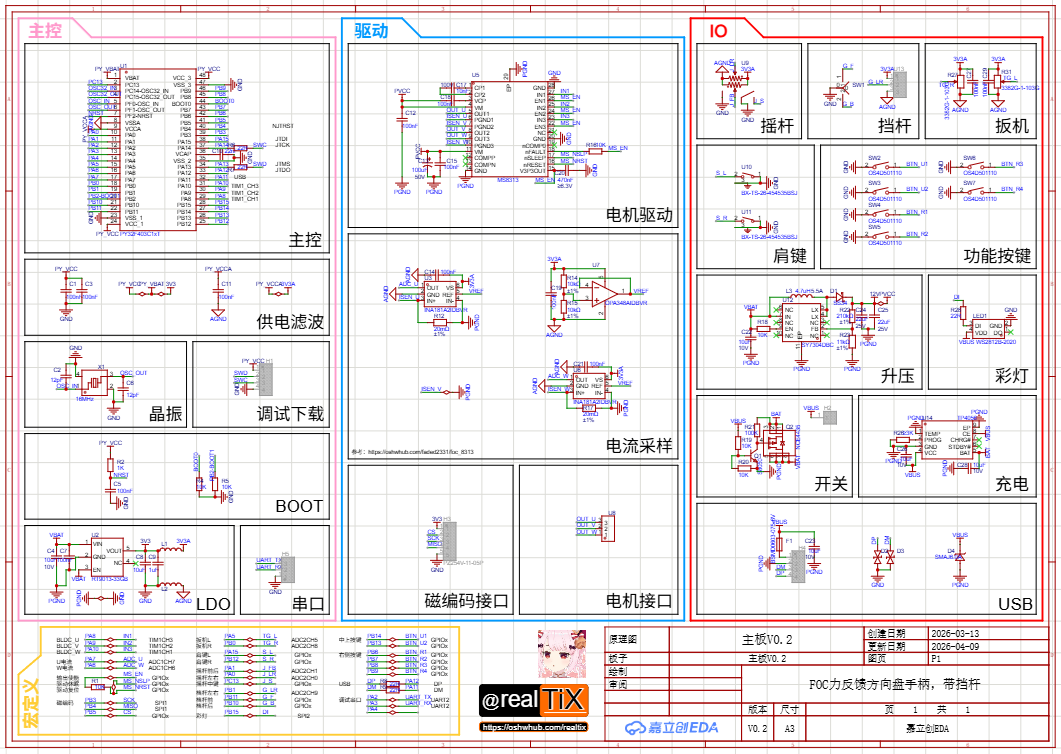

工程名称:FOC力反馈方向盘手柄,带挡杆 工程作者:realTiX 前言 小编今天逛开源平台,看到了一个很有趣的力反馈方向盘。 控制赛车非常丝滑**▼** 这这这,这是主打一个,在家也能实现“赛车”自由? 但这不是最重要的!最重要的是: 作者只用 1颗主控+1个10X7cm的主板PCB 就实现了 FOC+力反馈+USB HID全流程! 这是什么水平? 这是非常的有水平! 事情变得有趣起来了…… 这

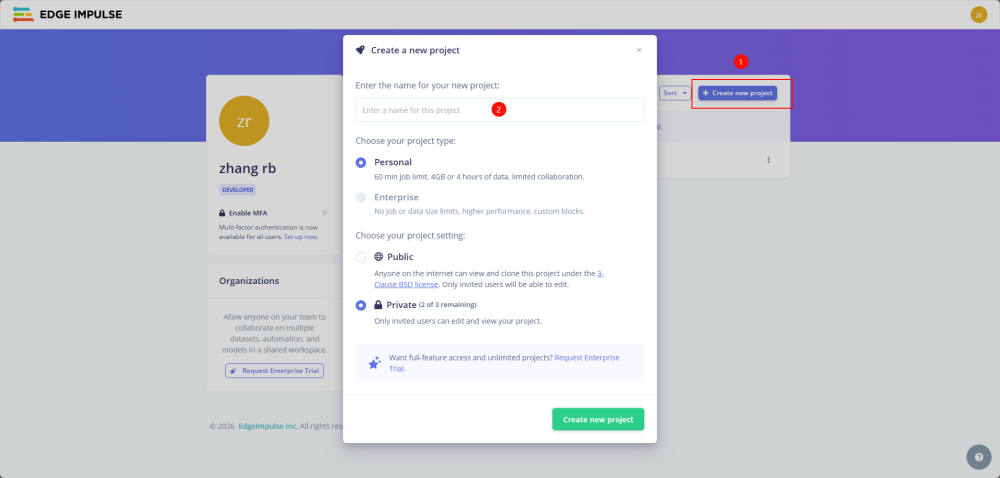

今天,将手把手带领学习如何训练一个语音关键词模型部署到嵌入式硬件上**,采用 Edgi-Talk 平台适配 Edge Impulse,**当然原理在其他的ARM嵌入式平台也是通用的。让我们看看如何让 Edgi-Talk 开始使用边缘机器学习! 目录 Edge Impulse 简介 创建账号 录制数据集 数据上传 数据分割 模型训练 模型评估 模型集成 1 Edge Impulse 简介 Edge

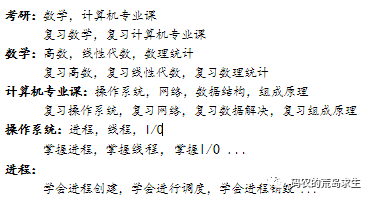

在讲解大型项目如何被构建之前,我们首先来讨论一个问题,有句话说的很好,梦想总是要有的,万一实现了呢,那么问题来了,要怎么实现呢,这里就涉及到了如何实现目标, 目标是如何实现的 其实很简单,本质上只有两点: 知道最后想要的是什么 为此需要做些什么 有时我们的目标可能不是简单的诸如每天跑五公里之类,比如像通过一门考试,学会一项技能这样的系统性工程。这时我们可能一下子不知道要做些什么,那么这就需要进

1. 前言 Verilog/System verilog 仿真中的时间单位/时间精度设置是保证仿真设置正确的重要手段,但是很多场景下却常常被忽视。设置不合理会导致诸多问题,例如延时不准确,时钟周期不对,打印信息不准确,验证用例耗费的时间特别长,多模块配合无法发现隐藏的问题。 因此,本文件将描述timescale、timeunit、timeprecision等概念,并描述如何正确地使用timesca

前言 在很多以太网、SATA 或其他高速接口项目中,我们经常会接触到 CRC(循环冗余校验)。通常,工程师会通过网站或软件工具生成一整套带异或操作的组合逻辑来实现 CRC 算法,而不去深入理解其原理——只知道可以这样用。事实上,在大多数情况下,确实不需要了解 CRC 的具体实现方法,这种黑盒化的使用方式在低频窄位宽场景下确实可行。 但是,当你的系统时钟非常高,例如 800MHz、1GHz,且数据位

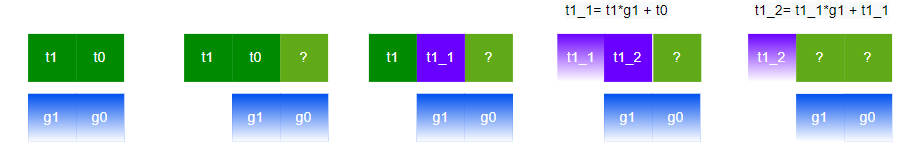

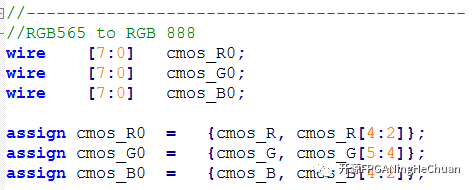

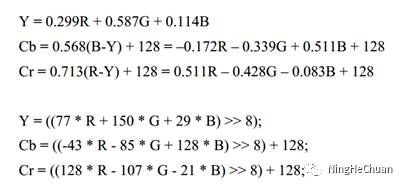

前面我们讲了基于FPGA用VGA显示一副静态图片,那么接下来我们就接着前面的工程来实现我们图像处理的基础算法里最简单的一个那就是彩色图像转灰度的实现。 将彩色图像转化为灰度的方法有两种,一个是令RGB三个分量的数值相等,输出后便可以得到灰度图像,另一种是转化为YCbCr格式,将Y分量提取出来,YCbCr格式中的Y分量表示的是图像的亮度和浓度所以只输出Y分量,得到的图像就是灰度图像了。我在这里选

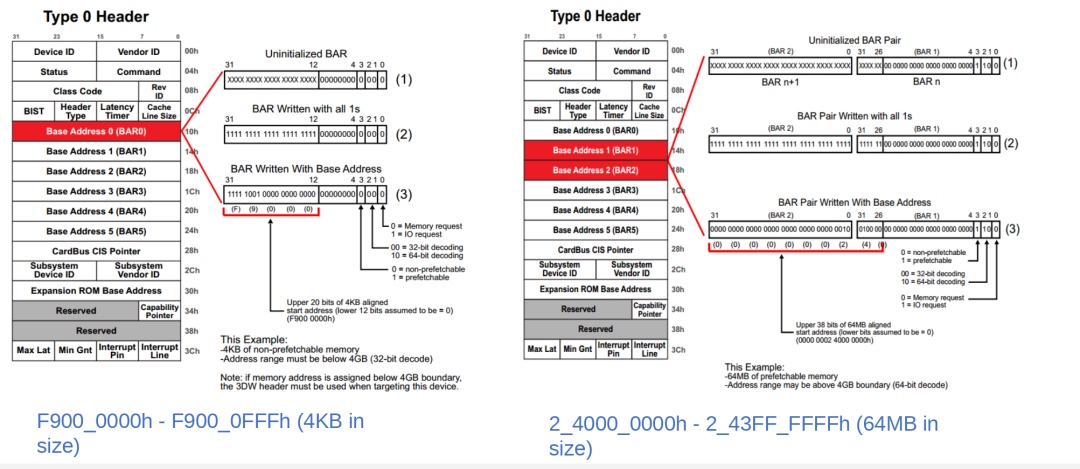

前言 对于主机而言,FPGA-PCIe 设备通过其 BAR(Base Address Register)被识别和访问。主机必须通过读写 BAR 所映射的地址空间,才能与 FPGA-PCIe 正确通信。这相当于将 FPGA-PCIe 内部的地址区域映射到主机的内存空间中,主机通过访问这段内存来完成数据收发。 readl(dif->bar0_mapped_addr + (offset<&l

之前学习了半年的图像处理,所以计划将自己学过的几个图像处理的基础算法,做过的设计记录下来,在OpenHW论坛上发表,计划是这样的,用VGA做显示,使用PC端上位机通过串口发送一幅图片数据到FPGA开发板,FPGA接收数据并做处理最终发送给VGA显示屏显示,计划要写的算法有彩色图像转灰度、均值/中值滤波、Sobel边缘检测等。那么现在这是第一篇,先来写VGA显示的驱动、以及将一幅图片显示到VGA显示

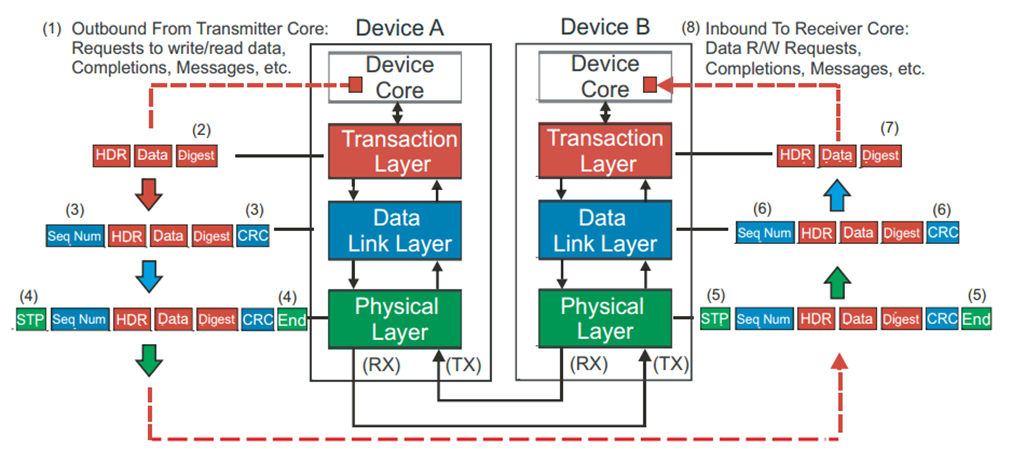

前言 本系列不会从零讲PCIe,也不会照搬规范条款,标准文档已经够厚,这里更像是一份工程师视角下的PCIe手边笔记 , 以更简洁的方式记录PCIe的关键点。 TLP包 由于PCIe-DMA的实现始终在事务层通过TLP包完成,因此深入理解TLP包的构成至关重要。 TLP包所在位置 在PCIe协议的传输层中,TLP包的结构相较于链路层与物理层的报文而言,最为简单清晰。 TLP的结构 TLP的结构

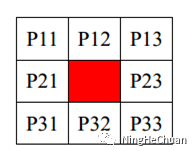

前面实现了基于FPGA的彩色图像转灰度处理,减小了图像的体积,但是其中还是存在许多噪声,会影响图像的边缘检测,所以这一篇就要消除这些噪声,基于灰度图像进行图像的滤波处理,为图像的边缘检测做好夯实基础。 椒盐噪声(salt & pepper noise)是数字图像的一个常见噪声,所谓椒盐,椒就是黑,盐就是白,椒盐噪声就是在图像上随机出现黑色白色的像素。椒盐噪声是一种因为信号脉冲强度引

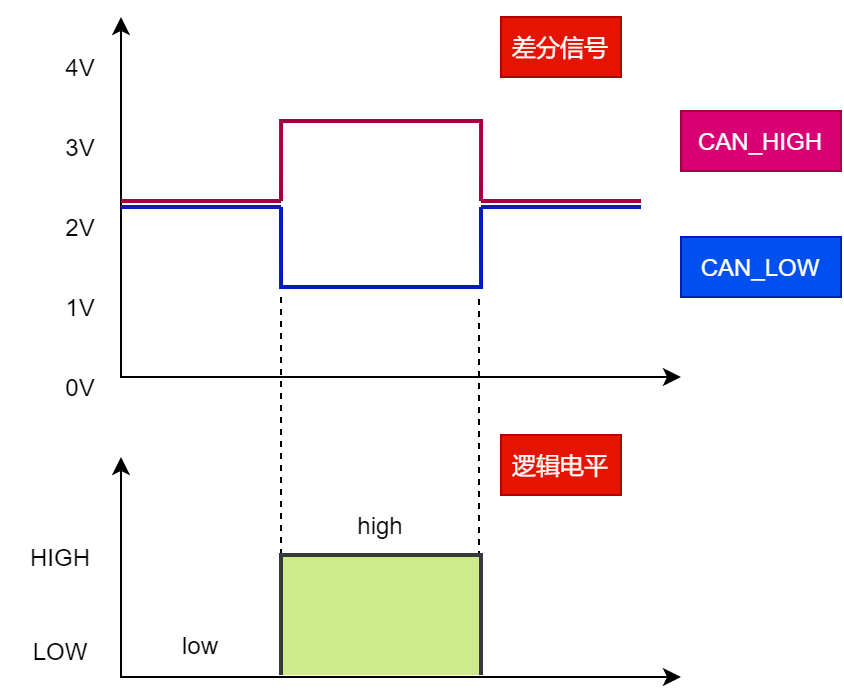

目录 什么是CAN总线? 物理层 差分信号 连接方式 CAN节点 CAN协议 如何寻址? 帧类型 数据帧 远程帧 错误帧 过载帧 消息时序以及同步 位时序 波特率 消息过滤器 如何配置? 总结 参考 什么是CAN总线? Controller Area Network,简称CAN或者CAN bus) 是一种功能丰富的串行

在上一篇文章中,我们已经带大家了解了多输入多输出(MIMO)能力的架构设计思路。 今天,小编将继续深入解析如何将架构设计真正落地到可运行代码,并带来一套可复用的核心实现。会介绍多输入多输出支持框架的关键组成部分。通过清晰的结构化设计、类型安全的接口抽象,为复杂的嵌入式 AI 模型建立一个高扩展性、高可维护性的基础底座。 下面,我们就将通过头文件设计、基础数据结构构建、生命周期管理等内容一步步展示一

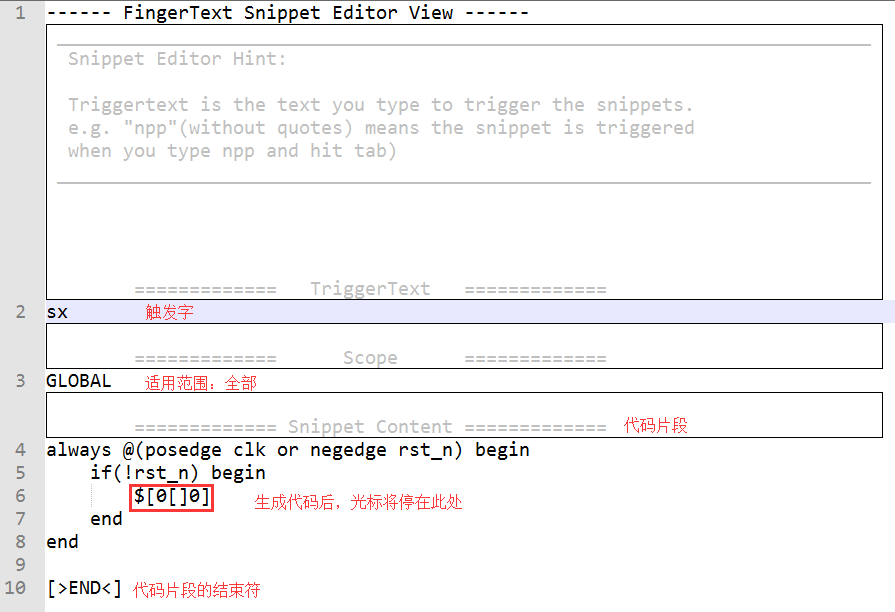

版本:Notepad++ 7.6.6 ,32位 //======================================================================== //== 安装与Verilog设置 //========================================================================

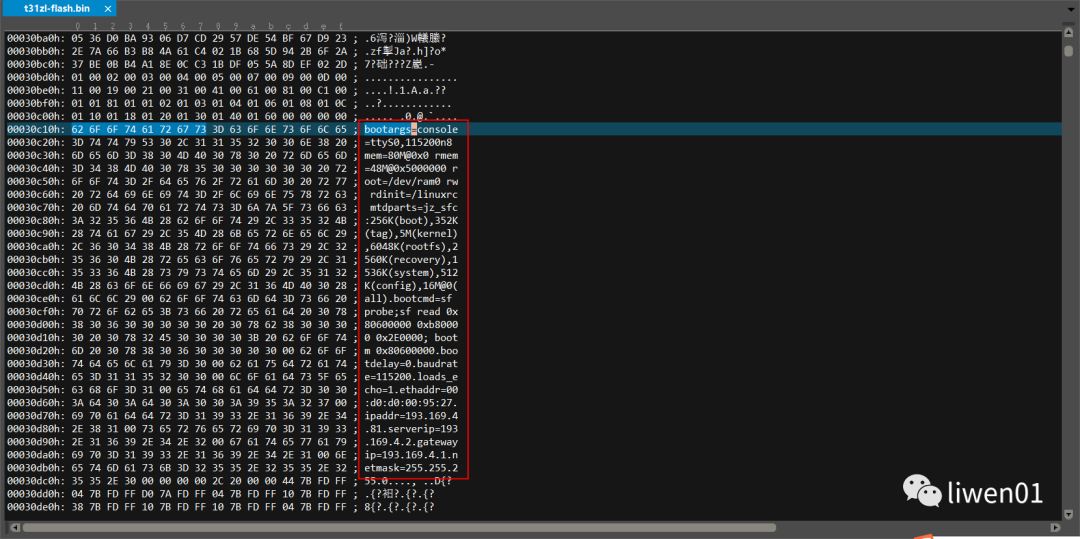

前言 在国内做产品设计开发,很难避免不被抄袭,被仿照。在没有形成技术壁垒之前,如何防止产品被抄袭是一个不可回避的问题。 (一)常规设备 常规设备主要的防护手段有: 专利保护 加密保护代码 授权校验 持续更新和改进 (1)专利保护 对于一些比较重要的技术发明或是创新,应该尽快申请专利。虽然目前国内对于知识产权保护的力度有限,但申请专利还是有用的,至少可以避免专利被别人提前申请,导致自己侵权。 (

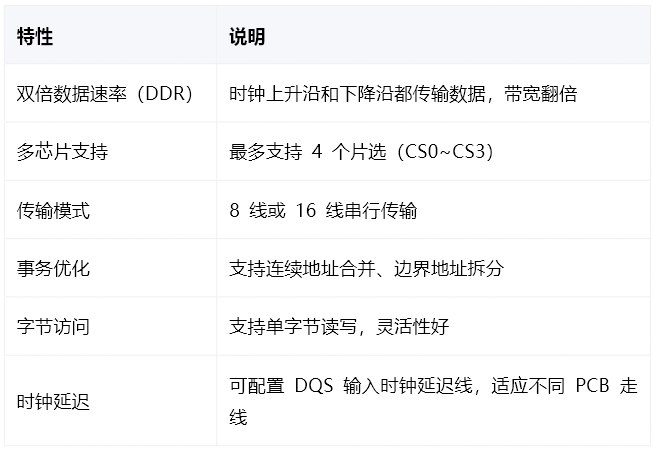

在工业控制和数据采集场景中,处理器与 FPGA 之间的高速数据交换是一个常见需求。传统方案通常采用 SPI(速度受限,一般 < 10Mbps)或 PCIE(带宽高但引脚多、设计复杂)。有没有一种方案,既能达到 几十 MB/s 的带宽,又只需要少量引脚,设计简单? 今天分享一个基于 睿擎派 RC3506 的方案——利用 RK3506 芯片内置的 DSMC(Double Data Rate Se

将彩色图像转化为灰度的方法有两种,一个是令RGB三个分量的数值相等,输出后便可以得到灰度图像,另一种是转化为YCbCr格式,将Y分量提取出来,YCbCr格式中的Y分量表示的是图像的亮度和浓度所以只输出Y分量,得到的图像就是灰度图像了。我在这里选择第二种方法实现。 YCBCr是通过有序的三元组来表示的,三元由Y(Luminance)、Cb(Chrominance-Blue)和Cr(Chrom