作为当前极紫外光刻技术的下一代演进,高数值孔径极紫外光刻(High-NA EUV)正从研发走向量产准备。它并非现有0.33 NA EUV的简单升级,而是通过将数值孔径提升至0.55,为2纳米以下逻辑节点和先进DRAM的关键层图形开辟新的工艺窗口。

技术原理与核心优势

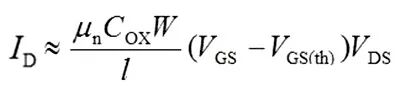

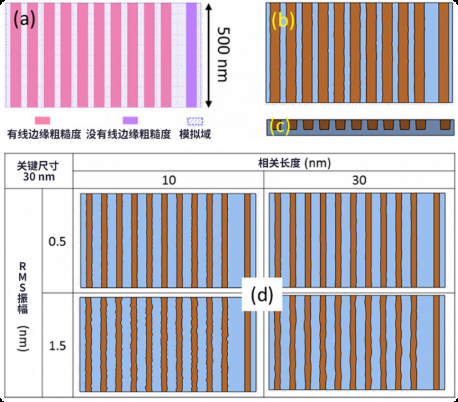

High-NA EUV仍使用13.5nm波长的EUV光源,但将投影光学系统的数值孔径从0.33提高到0.55。根据瑞利准则,分辨率与NA成反比,因此这一提升直接带来了分辨率的革命性进步:理论极限可解析16nm间距的线条/空间图案。2024年,imec与ASML在联合实验室中已成功实现16nm间距线条/空间的单次曝光成像,创造了世界纪录。

更高的数值孔径还意味着投影透镜能捕获更多衍射级次的光,显著提升成像对比度。实验证明,这能使局部关键尺寸均匀性改善18-42%,并降低约60%的曝光剂量,直接提升生产效率。

这项技术最有价值的产业意义在于:它有机会将很多原本依赖复杂多重图案化的关键层,重新拉回到单次曝光。每多一次图案化,就意味着更多掩模、更多套刻风险、更多循环时间和缺陷机会。对于未来A14/A10逻辑节点的最复杂金属层,传统0.33 NA EUV需要3-4次曝光,而High-NA方案可通过单次曝光实现。同样,对于下一代DRAM节点的关键位线外围/存储节点接触层,也可从至少三次曝光减少为一次曝光。

带来的系统性改变

High-NA EUV不仅改变分辨率,还改变了设计方式。过去先进逻辑层的设计越来越偏向一维、单向布线,是因为制造约束迫使设计自由度向光刻极限让步。更高的分辨率使芯片设计可以回归更高效的布局,例如实现双向布线和曲线几何设计。imec开发的方法可在放松关键间距的同时实现20%的面积缩减,使设计人员能更自由地优化功耗、性能和面积。

同时,这项技术改变了制造复杂度的分布。步骤减少意味着循环时间更短、套刻风险更低、缺陷机会更少,工艺耦合也更容易收敛。先进制造中,“更少的步骤”本身就是良率与成本优势的重要来源。

面临的关键挑战

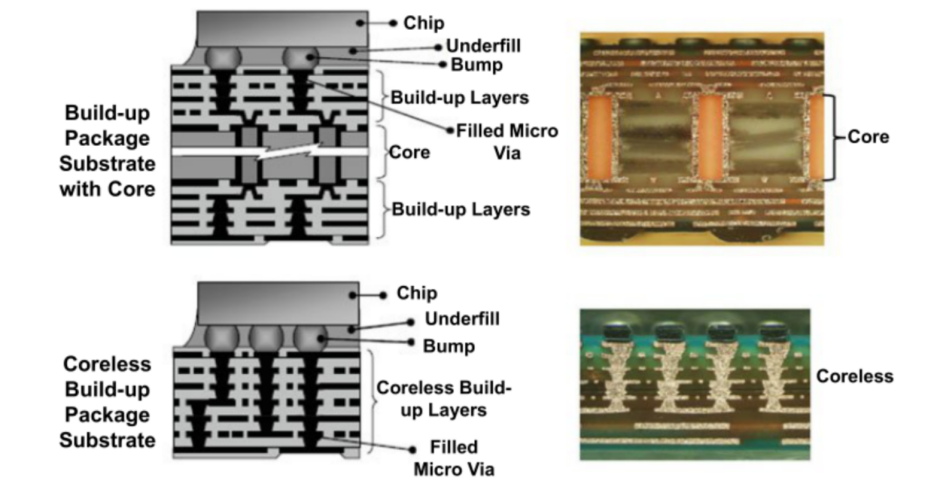

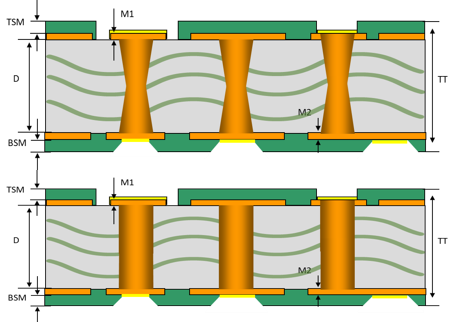

High-NA EUV在推进过程中也面临严峻挑战。首先,焦深大幅缩小,比0.33 NA系统小2-3倍,迫使使用更薄的光刻胶,并对晶圆平整度提出极致要求。其次,随机缺陷控制仍是核心挑战——尺寸越小,光子统计、材料反应和边缘粗糙度越敏感,良率相关缺陷不会因NA提升而自动消失。此外,采用变形镜头导致单次曝光区域缩小,需要通过场拼接技术来制造大芯片,这对套刻精度提出了新考验。

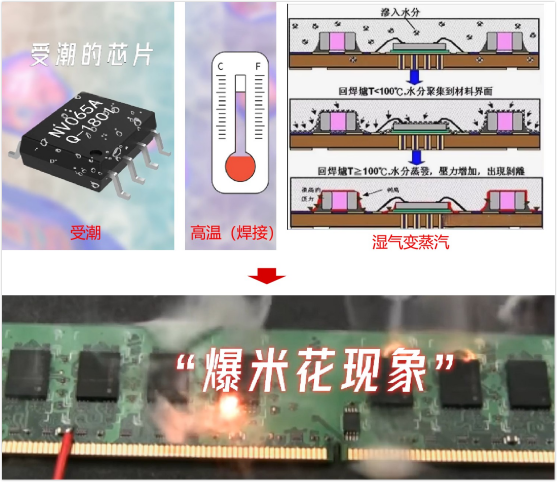

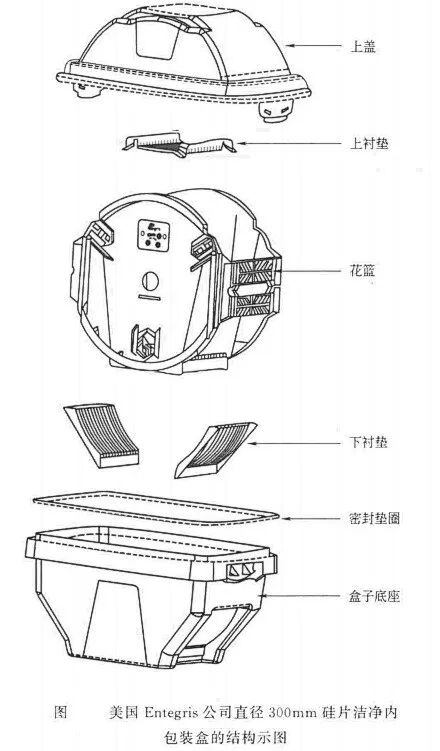

材料体系必须同步升级。光刻胶、掩模、底层材料、刻蚀与计量方法都要跟上。High-NA从来不是一台设备单独就能成功的技术,而是需要全产业链协同优化的结果。

发展现状与导入路径

ASML与imec的High-NA EUV联合实验室于2024年在荷兰正式运营,配备了首台原型扫描仪EXE:5000及完整配套设施,为芯片制造商、设备商和材料供应商提供早期开发环境。预计在2025-2026年期间投入大规模制造,首批应用将聚焦于14A逻辑芯片的临界金属层和D0a DRAM的关键层。

从产业导入路径看,High-NA不会一夜之间取代现有0.33 NA EUV。更现实的情形是:在相当长的时间内,低NA与高NA会按层级、按成本、按缺陷敏感度并行存在。真正决定技术插入的,从来不是“理论上谁更先进”,而是哪一层必须用它、哪一层继续沿用原方案更划算,以及整体良率与成本能否闭合。

评论区

登录后即可参与讨论

立即登录