随着多芯片模块(MCM)复杂度的提升,已知好芯片(KGD)技术成为保障成品率的核心。单芯片合格率的微小差距将对模组良率产生指数级影响。本文深度解析KGD筛选的四大路径,对比压力接触与金属化连接等测试技术,并前瞻AI与3D封装驱动下的协同创新。

在半导体封装领域,已知好芯片(KGD)技术作为提升多芯片模块(MCM)成品率的核心支撑,其发展路径始终围绕“高合格率芯片筛选”与“高效缺陷检测”两大主线展开。

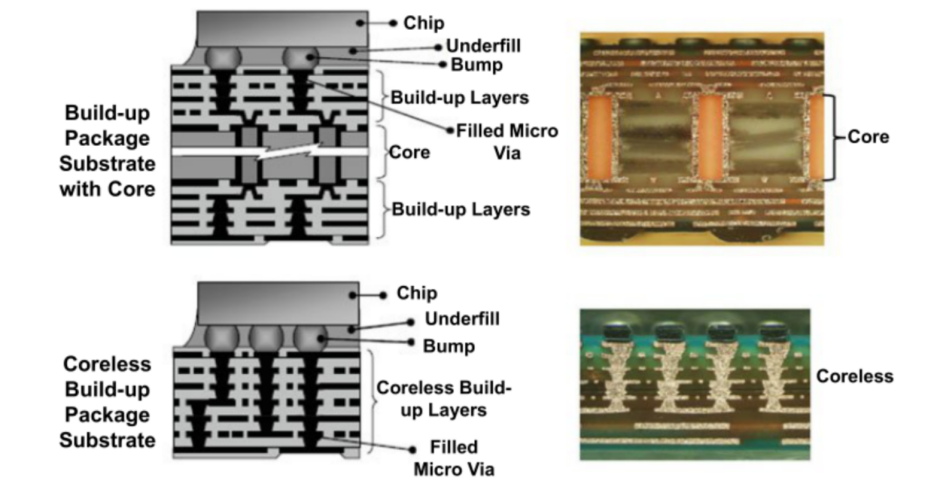

传统封装后测试体系虽已成熟,通过DIP、PLCC、PGA等封装形式的专用插座可实现全功能、全温域、全频率的可靠性验证,配合老化试验可剔除初期致命缺陷,使封装块合格率达0.99999以上。

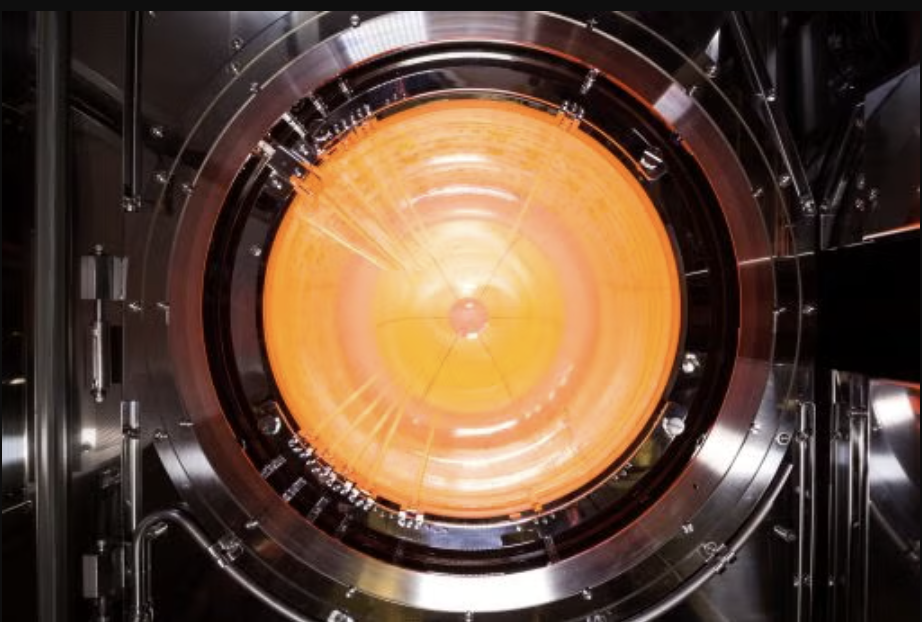

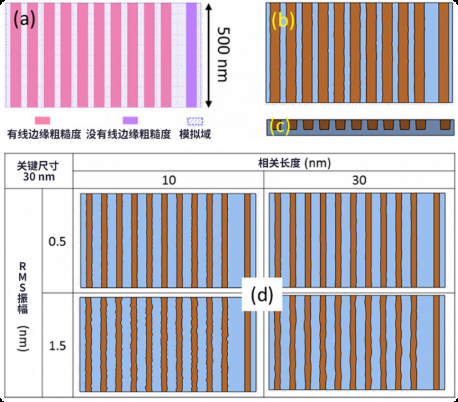

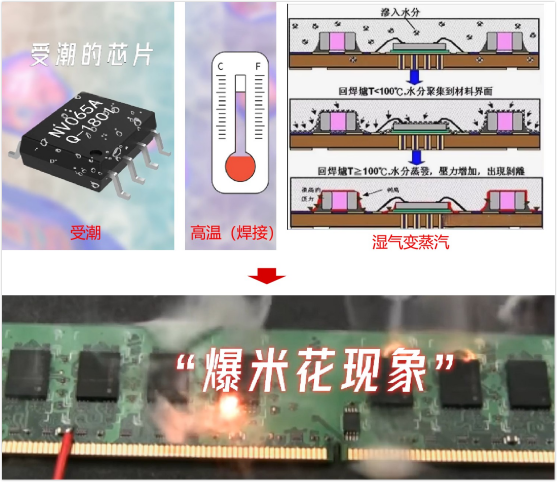

然而,未封装芯片的测试面临根本性挑战——圆片探针测试仅能覆盖有限参数,难以在宽温域下保持晶圆一致性,且探针损耗、接触电阻、散热限制及信号衰减等问题导致测试覆盖率不足,成品率仅0.50~0.99,较封装块低数个数量级,直接制约了MCM模块的成品率表现。

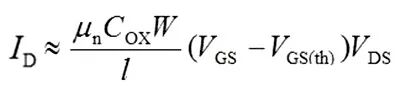

MCM成品率模型揭示了多部件组装的质量控制逻辑:基础公式

Ym\=100(Pc)ᴺ

表明,当模块集成N个芯片时,若单芯片合格率Pc未达0.999,模块成品率将随芯片数量增加呈指数级下降。

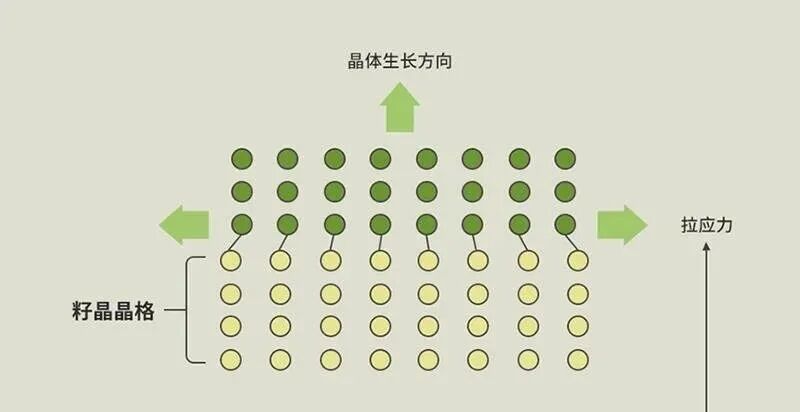

当前,提升KGD合格率的路径已形成四大技术方向:工艺法通过6σ工艺控制实现晶圆级筛选,从源头提升良率;设计法通过内建自测试(BIST)与边界扫描结构增强芯片可测性,支持预分类与缺陷定位;统计取样法通过单芯片组装测试对批次进行合格性验证;全芯片测试法则利用圆片探针、TAB或微带载体对每片芯片进行全参数测试,其有效性取决于环境应力施加精度与缺陷电气特征识别能力——需在避免合格芯片寿命退化的前提下,通过温度循环、电压应力等手段激发缺陷,结合动态参数测试实现精准筛选。

行业实践中,KGD技术的应用正朝着标准化与成本优化演进。一方面,芯片制造商联合体正推动多芯片封装标准的统一,促进不同类型未封装芯片的多用性研究;另一方面,针对不同合格率等级(如0.9、0.99、0.999)的定量处理方法逐步完善,配合供应商与用户共担的成本价格结构,形成可持续的商业模式。

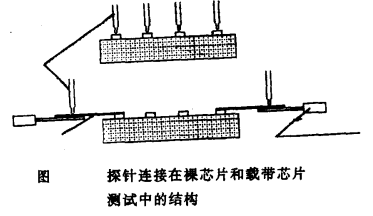

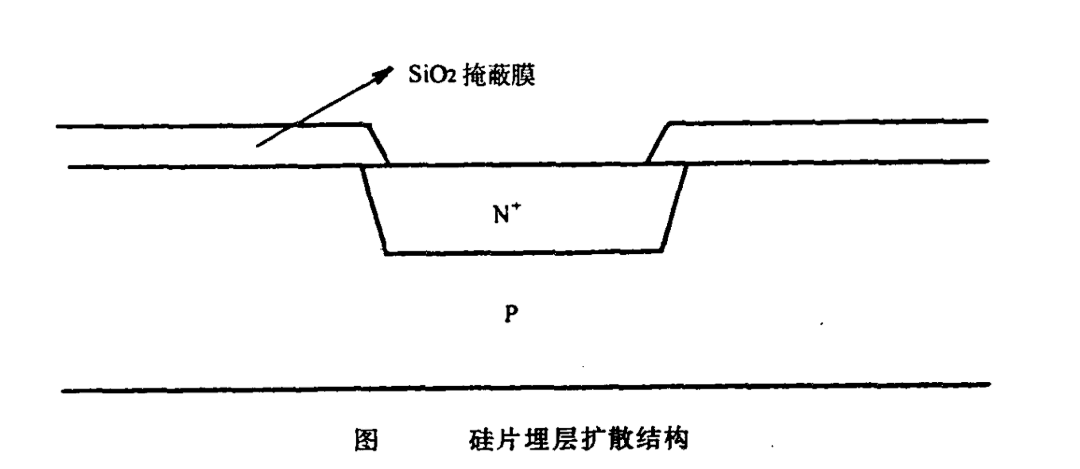

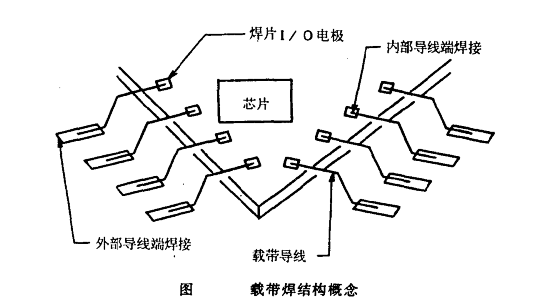

使用压力与芯片焊点形成接触的测试方法

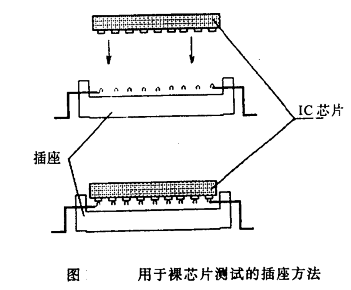

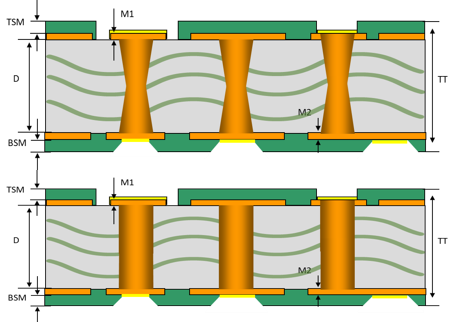

在混合微电路及多芯片模块(MCM)组装中,未封装集成电路的测试筛选技术始终围绕“低损伤接触”与“高精度缺陷识别”两大核心需求演进。传统统计取样法虽通过封装部分芯片进行测试以评估整批合格率,但受限于高成本与有限精度,其确定合格率通常仅达0.90左右,即便结合成品率改进方案,也难以突破0.95的瓶颈,难以满足高可靠性场景需求。当前,基于压力接触的测试方法正通过技术创新突破传统限制,其中探针插板技术通过可定位探针测试台实现冷热环境下的芯片级测试,但需解决接触电阻衰减与焊点损伤问题,类似圆片探卡测试的挑战仍需通过微型金凸点制造与精确对位技术优化。

插座技术虽长期被视为理想方案,却因焊接点损伤、高频性能受限及成本高昂等问题进展缓慢,近年来微接触点技术的突破为平坦化对准与压力接触区域扩展提供了新思路,尤其在钝化层下凹陷孔腔的接触优化方面取得进展。

各向异性导电材料的应用正成为热点方向:各向异性导电橡胶膜(ACCF)通过垂直方向导电、水平方向绝缘的特性,在20μm间距接触点对准与低阻压力接触维持方面持续优化,已拓展至倒装芯片与裸芯片直接测试场景;各向异性导电粘性膜(ACAF)则通过导电微粒(10-20μm直径)的z轴导通特性,结合热膨胀与腐蚀机理控制,实现长期可靠性,其可逆固化特性支持预测试后芯片的轻松分离与再处理,在TAB及裸芯片测试中展现出低损伤、高精度的优势。

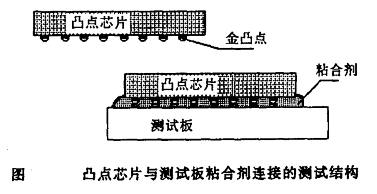

凸点倒扣粘接技术通过金、铜、铟、锡-铅合金等凸点材料与可分离粘合剂的组合,在压力接触下实现临时互连,尤其适用于倒装工艺的MCM制造商,兼顾经济性与可操作性,但需平衡额外处理成本与定位装置精度。圆片探针法针对大批量生产IC,通过多层布线技术实现总线连接与信号处理,结合倒扣对位粘接进行老化测试,关键在于坏芯片的有效隔离与测试效率提升。

与集成电路焊点进行金属化连接实现预先测试

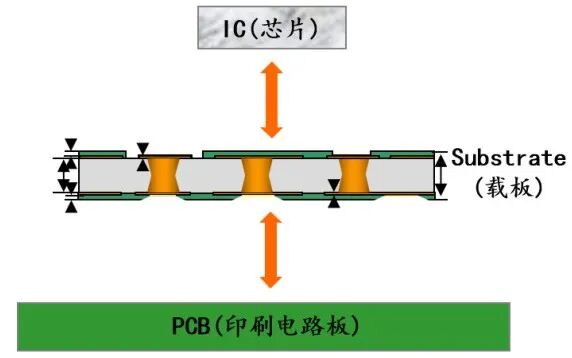

在集成电路预先测试领域,金属化连接技术通过形成稳定的电气互连,为高可靠性筛选提供了传统压力接触方法之外的补充路径,其核心在于平衡连接强度、损伤控制与成本效益。丝焊键合临时封装测试作为早期KGD筛选方案,虽依托成熟热键合、超声键合技术实现芯片临时封装与性能验证,但受限于生产效率低、载体成本高及芯片取出损伤风险,难以大规模应用,需通过自动化丝焊设备与可剥离临时载体材料优化,降低操作成本与损伤概率。载带自动键合(TAB)技术凭借小型化、自动化优势,在微间距I/O连接中展现高可靠性,其标准载带结构为较大焊点提供便捷引出端,适配标准测试装置,已成功应用于部分MCM场景,但高昂的设备成本与次级结构成熟度不足限制了普及,需通过引线金属标准化(如Cu、Al、Ti/Ni体系)、键合工艺优化(焊料回流Au/Sn低共熔体、Au/Au热压合、激光辅助键合)及成本模型重构,推动产量提升与成本下降,同时需解决老化变形、键合再现性等规范化技术问题。

倒装芯片与一次性测试架键合通过芯片凸点处理与测试架凸点制造,结合焊料回流、低温共熔等金属化连接方法实现临时互连,虽能降低接触电阻,但电极损伤风险较高,需通过软焊料凸点探针测试、圆片阶段老化试验等技术优化,减少二次损伤,同时需关注凸点材料(如金、铜、铟、锡-铅合金)的可靠性及键合工艺参数控制。微芯片支架(MCC)技术通过玻璃/环氧树脂、陶瓷、硅片或氮化铝等材料载体,结合导线键合、载带焊或倒装芯片法实现集成电路与支架互连,支架与衬底间可采用多种连接技术(导线键合、载带贴装、凸点倒装等),其优势在于提供标准化测试平台,支持多种集成电路的兼容测试,需通过材料性能优化(如热膨胀系数匹配)、互连工艺标准化及成本效益分析,提升应用范围与经济性。带状线上芯片技术通过TAB系统与集成电路导线键合,结合环氧树脂涂覆与老化测试,利用通用TAB设计方案容纳不同结构集成电路,避免定制化内引线键合的高成本,需通过备用I/O线规划、自动化处理系统优化,提升测试效率与灵活性,同时需关注导线键合可靠性及涂覆材料性能。

近年来,金属化连接技术正与新兴技术融合,如纳米金属浆料、柔性金属复合材料提升互连导电性与机械稳定性;AI驱动的键合路径规划与参数优化算法,实现键合质量实时监测与动态调整;3D封装场景中,垂直互连金属化层通过嵌入式传感器监测电性能与热性能,确保KGD在复杂结构中的可靠性;自动化机器人与视觉定位系统集成,实现芯片与测试装置的亚微米级精确对准,结合力反馈控制技术动态调整键合压力,降低电极损伤风险,提升测试重复性与良率。

这些技术的协同创新,正推动金属化连接测试筛选向“高精度、低损伤、低成本、高兼容”方向演进,为MCM及混合微电路在高性能计算、航空航天等高可靠性领域的广泛应用提供坚实支撑,确保其在成本与性能上持续领先传统封装技术。

评论区

登录后即可参与讨论

立即登录