当AI从云端向边缘和终端设备迁移,一场以“端侧AI”(Edge AI)为核心的技术应用革命正悄然到来。

在这场变革中,我们必须思考的是,数十亿乃至数百亿台终端设备的未来发展方向——特别是打破它们依赖云端连接才能运行AI任务的固有模式。这些设备必须成为真正具备AI能力的端侧系统,能够以更高效率执行端侧推理,其计算能力以每瓦特所能达到的万亿次运算次数(TOPS/W)来衡量。

与AI数据中心不同,对于端侧实时推理,业界强烈推动在更靠近数据产生的地方(即设备端)实现AI加速。但与此同时,端侧AI也带来了新的挑战:除了算力不足之外,还必须考虑内存性能,并且严格限制每个用例的能耗和成本。这些限制凸显了一个越来越清晰的现实:在构建任何高效的端侧AI解决方案时,计算能力与内存资源正逐步成为同等重要的关键构成要素。

更值得关注的是,曾经仅作为数据“仓库”的存储芯片,正被赋予“计算使命”——不再只是被动地保存代码与参数,而是成为端侧AI推理的“神经中枢”与“算力引擎”。如今,传统冯·诺依曼架构下的“内存墙”与“功耗墙”挑战,正推动业界探索两大方向:一是通过不断迭代传统架构下的存储性能,以及探索开发新的存储载体;二是转向更高效的计算架构(存算一体化),以实现计算与存储的融合。

本文将深入剖析这一应用变革,重点从存储硬件载体、架构演进出发,探讨产业界如何应对端侧AI带来的机遇与挑战,并展望存算一体等颠覆性技术的应用前景。

“存储墙”:端侧AI的“阿喀琉斯之踵”

端侧AI是指将AI模型的训练或推理过程直接在数据产生的源头——即物理世界中的终端设备上执行,而无需将数据发送到云端数据中心。这些设备涵盖了智能手机、智能摄像头、自动驾驶汽车、工业物联网(IIoT)网关、可穿戴设备乃至家用电器(图1)。

图1:端侧AI应用场景示意图。(来源:Apple、DJI、TP-LINK)

端侧AI的崛起并非偶然,而是由一系列实际需求驱动的必然趋势:

1.实时响应性:自动驾驶、工业机器人等应用场景对决策延迟的要求达到了毫秒级,将数据远距离传输至云端再返回结果的模式无法满足需求。

2.数据隐私与安全:在本地处理个人健康数据、面部识别信息等敏感数据,可以有效避免数据在传输和云端存储过程中被截获或滥用的风险。

3.网络带宽与成本:随着高清视频流、激光雷达等传感器产生的数据量爆炸式增长,持续依赖云端传输会消耗巨大的网络带宽,并产生高昂的运营成本。

4.连接可靠性:在网络连接不稳定或中断的环境下(如偏远地区的设备或移动中的车辆),端侧AI能够保证核心功能的持续运行。

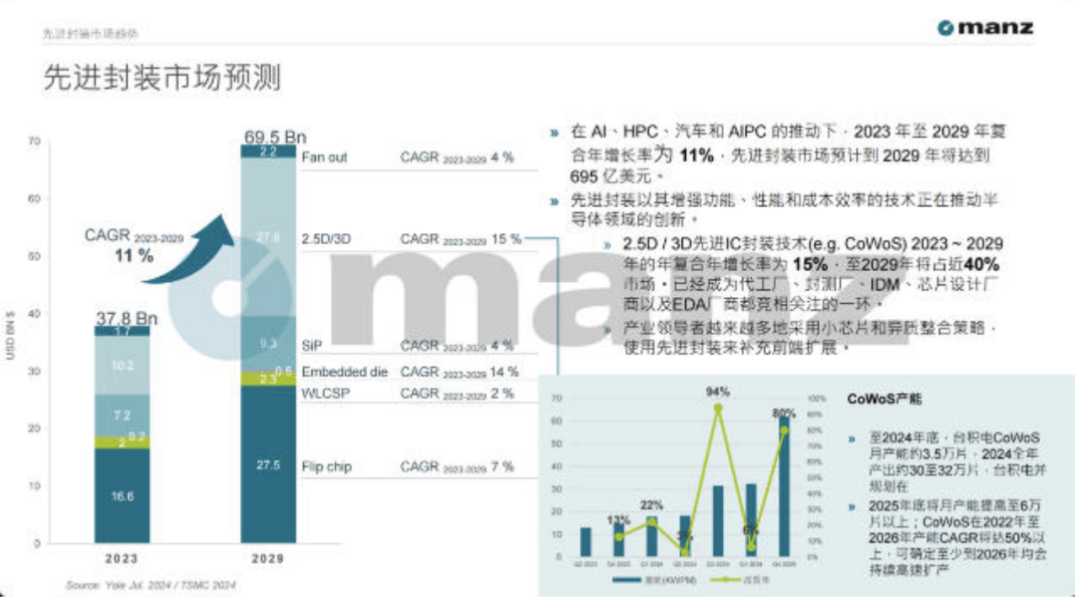

据Fortune Business Insights预测,全球边缘AI芯片市场正经历高速增长。2025年,全球边缘人工智能市场规模为358.1亿美元。预计该市场将从2026年的475.9亿美元增长到2034年的3858.9亿美元,预测期内复合年增长率为33.30%。这一巨大的市场潜力正吸引着全球半导体厂商的目光。

然而,AI算法的强大能力建立在海量数据和复杂模型之上,这给传统的、基于冯·诺依曼架构的计算系统带来了严峻挑战。冯·诺依曼架构的核心特点是计算单元(CPU/GPU/AI加速器)与存储单元(DRAM/闪存)在物理上分离,二者通过数据总线连接。在AI应用中,这意味着模型的权重参数和待处理的数据需要在存储和计算单元之间频繁地来回搬运。

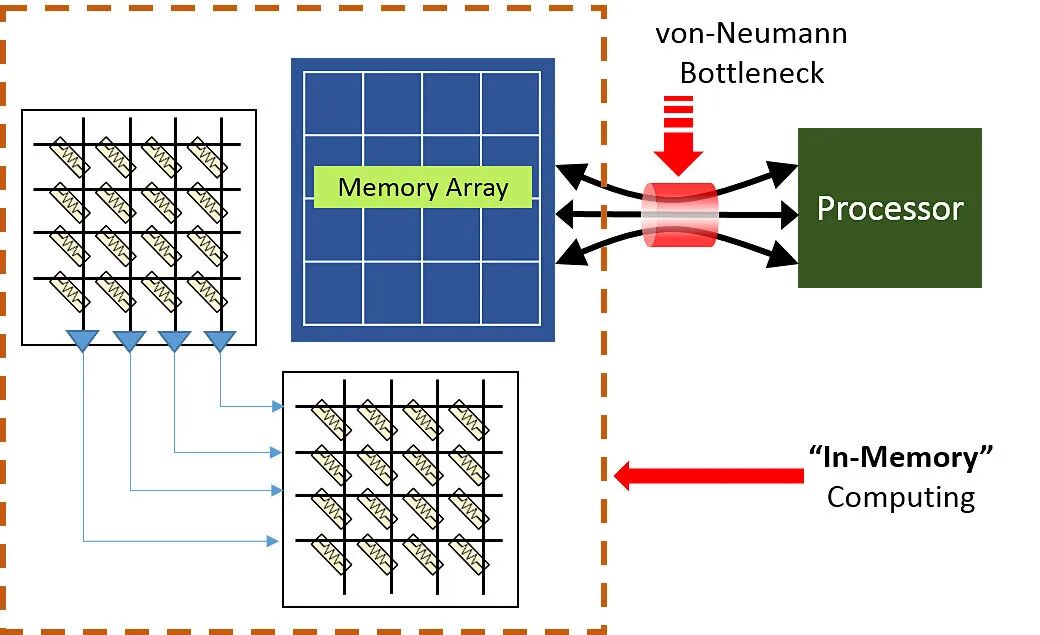

这种分离式架构导致了两个核心问题,统称为“冯·诺依曼瓶颈”(图2):

1.功耗墙:研究表明,在现有CMOS工艺下,数据搬运所消耗的能量远高于计算本身。将一个数据从DRAM移动到计算核心的能耗可能是执行一次浮点运算的数百甚至上千倍。在功耗预算极其有限的端侧设备中,这种能量开销是不可接受的。

2.存储墙:过去几十年,处理器的性能以远超内存带宽和延迟改善的速度增长。这种性能差距形成了所谓的“存储墙”。AI加速器即使拥有高达每秒数万亿次(TOPS)的理论算力,但如果存储系统无法及时“喂饱”数据,其大部分时间都将处于空闲等待状态,导致实际性能大打折扣。

图2:传统架构因数据搬运受限于“冯·诺依曼瓶颈”;存内计算将运算移至存储内部,降低能耗、提升效率。(来源:普渡大学)

美光科技工业业务部门高级细分市场营销经理Wil Florentino形容这一问题:“这就像造一辆搭载500马力发动机的汽车,却使用了低辛烷值汽油,以及性能不佳的轮胎。无论发动机多么强劲,汽车的整体性能都会受到系统中性能最差部件的限制。”

对于端侧AI而言,“存储墙”问题尤为突出。一方面,AI模型(尤其是生成式AI模型)的参数量持续膨胀;另一方面,端侧设备受限于成本和物理尺寸,无法像服务器那样配置海量的、高速的内存。因此,存储系统已然成为制约端侧AI性能、功耗和成本的关键瓶颈。

存储技术如何应对端侧AI挑战?

面对端侧AI的挑战,存储技术正沿着两条路径演进:一是传统技术的持续优化和适配;二是颠覆性新兴技术的商业化落地。

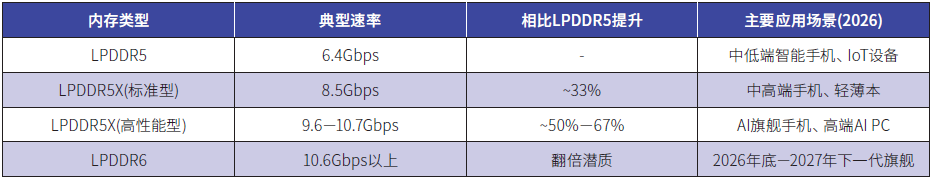

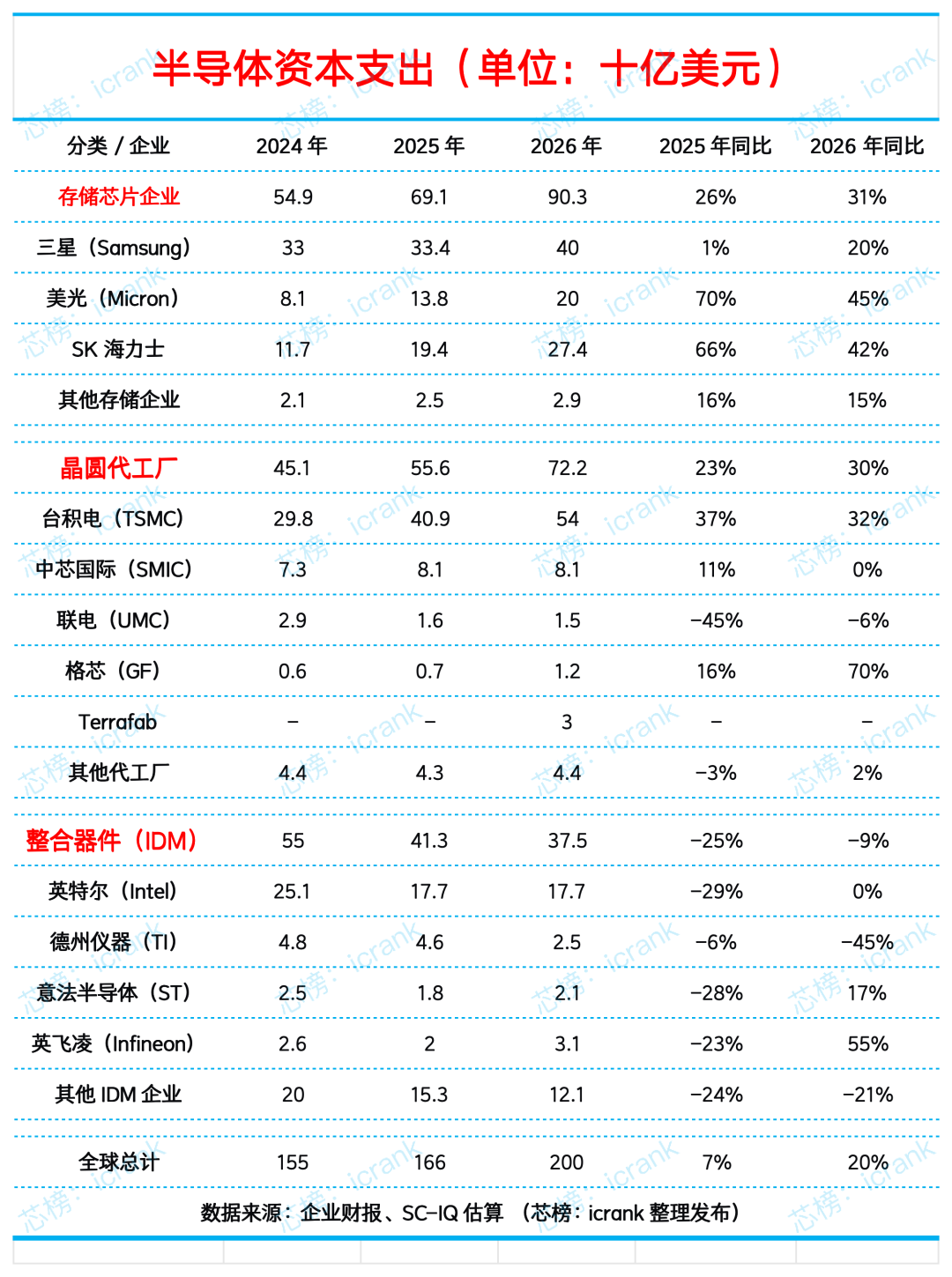

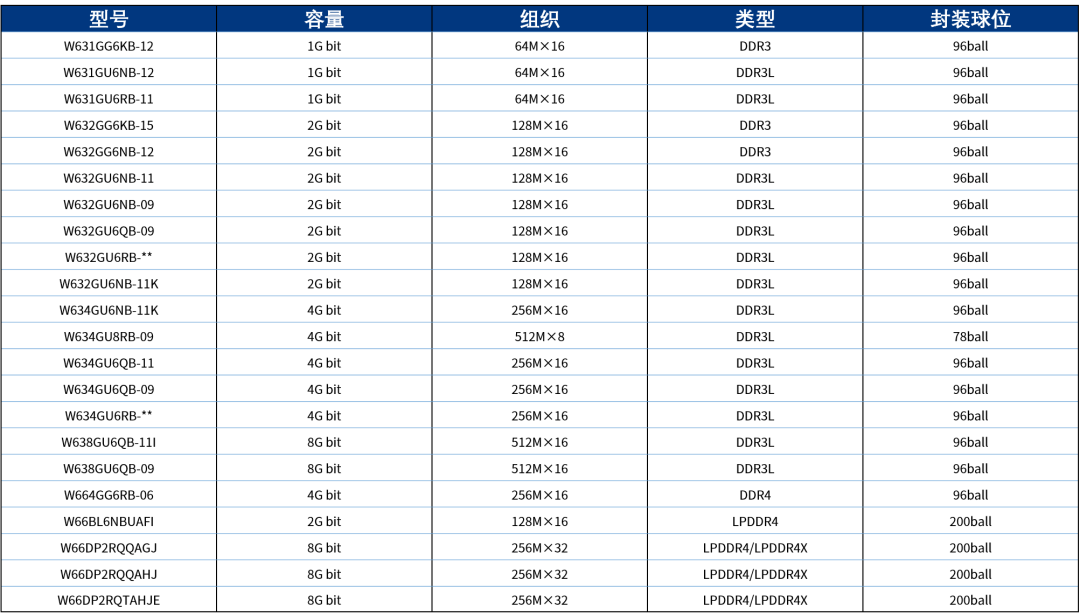

作为当前端侧设备中最主流的工作内存,DRAM技术仍在不断迭代,其中专为移动和低功耗场景设计的LPDDR(Low-Power Double Data Rate)系列是主力军。LPDDR5X被誉为端侧AI的“高速公路”,是中高端智能手机、AI PC和高端边缘计算平台的主流选择。目前,美光等厂商推出的LPDDR5X内存,已实现高达9.6Gbps的峰值带宽,这一速率相比初代LPDDR5(6.4Gbps)提升了约50%。同时,它通过优化信号完整性和1β等先进工艺,显著降低了数据传输的延迟,满足了端侧生成式AI(如手机端LLM)对频繁、小规模数据交换的高吞吐需求。据悉,Galaxy S26 Ultra将搭载更先进的10.7Gbps LPDDR5X内存。

AI的下沉不仅体现在手机和PC上,更延伸至AR/VR眼镜等新兴的头戴设备。集邦咨询邱宇彬在MTS2026存储产业趋势研讨会上描绘了AR眼镜的六大应用场景,从实时翻译到健康监控,无不依赖于对周围环境的实时感知和快速响应。这对存储提出了前所未有的挑战:超薄、小型化、大容量、高速度。为此,深圳时创意通过采用先进的SDBG隐切工艺和C-Molding技术,成功推出0.6mm超薄ePOP存储产品,并实现LPDDR5X在AI眼镜上的量产。

表1:LPDDR5系列与LPDDR6总结对比表(2026)。(来源:根据公开资料整理)

2025年7月,JEDEC协会正式发布了LPDDR6标准(表1)。LPDDR6的起始速率预计将突破10.667Gbps,最高可达14.4Gbps以上。预计,2026年是LPDDR5X的性能巅峰期,同时也标志着行业开始向LPDDR6架构进行技术平移的准备期。

尽管LPDDR系列性能不断提升,但其作为易失性存储(断电数据丢失)和基于冯·诺依曼架构下的独立组件,其本质并未改变。它仍然面临着刷新功耗、数据搬运开销等固有问题。特别是随着工艺微缩至1β或更先进工艺,存储单元越发微小,漏电风险增加,导致刷新频率必须更高。这使得在待机状态下,刷新功耗占据了系统功耗的很大比例,违背了移动设备对长续航的追求。

对于端侧AI而言,存储不仅要大,加载速度(读取带宽)也必须足够快,以实现“无感”启动AI应用。近年来,以LPDDR5X(内存)和UFS 4.0(闪存)为代表的新一代移动存储标准,通过紧密的协同进化,构成了支撑端侧大模型运行的“性能铁三角”的另外两极(另一极为SoC)。

UFS 4.0/4.x目前是2026年主流旗舰的核心存储方案,支持高达4.3GB/s的读取速度。这意味着加载一个30亿参数的AI模型只需不到0.5s。这主要得益于它极高的顺序读取性能,能快速把模型数据从存储搬到内存里,为端侧AI运行扫清了关键障碍。近期,铠侠就已宣布向客户UFS 4.1闪存样品,其性能全面升级,随机读取性能飙升90%,可满足端侧AI设备对大容量存储的迫切需求。

同样,JEDEC已于2025年末定案UFS 5.0标准。2026年开始有首批产品送样,如美光科技已针对基于1γ工艺的LPDDR6等移动DRAM产品送样。其理论速度翻倍至10.8GB/s,并针对AI密集型数据访问路径进行了专门优化。预计搭载该标准的终端将在2026年底至2027年初面世。

而在轻量级端侧AI(如智能穿戴、工业传感器)中,NOR闪存的需求量也将因AI固件代码量的增加而显著提升。

值得关注的是,端侧AI(如手机本地运行大模型)对内存带宽的需求激增,传统的LPDDR5X/6已逐渐难以满足每秒数兆次的Token生成速度,这倒逼了存储架构的革命。未来几年,高带宽内存(HBM)在端侧的应用将是利基市场。尽管HBM涉及复杂的3D堆叠、TSV制造和2.5D先进封装,成本极高,与端侧设备的价格敏感性背道而驰,但在面向需要极致性能的高端边缘设备,如车载计算平台、高端旗舰智能手机(2027年20周年纪念版iPhone被传将引入HBM)、高端工业自动化网关等,仍将有一定的市场空间。

业界普遍认为,2026年是“移动HBM”实现初步商业化的关键一年。目前,存储巨头都在积极推进HBM技术的迭代(比如,三星和SK海力士就分别开发了VCS和VFO技术,以实现移动HBM的量产;SK海力士的HBM2E已用于谷歌旗下的Waymo自动驾驶汽车),并探索集成处理内存(PIM)能力,以进一步减少数据搬运。这些技术探索可能为未来更高集成度的端侧AI芯片提供借鉴。

此外,新兴非易失性存储器(NVM)是解决端侧AI存储痛点的关键变量。它们不仅能在断电后保存数据,还具备传统闪存所不具备的高速、低功耗和高耐久性等优点,使其成为替代部分SRAM和DRAM、并与AI计算深度融合的理想选择,比如阻变存储器(ReRAM)、磁性随机存取存储器(MRAM)等。

存算一体:让数据“就地思考”

如果说主流与新兴NVM是在“优化”冯·诺依曼架构,那么存算一体(CIM)则是在“颠覆”它。

对此,时创意董事长倪黄忠在MTS2026存储产业趋势研讨会上指出:“2023年是一个关键的转折点。随着AI大模型推理的规模化落地,‘以存代算’成为行业共识,标志着存储角色的根本性转变。存储不再只是AI算力体系中可有可无的配套组件,而是从幕后走向台前,跃升为降本增效的核心路径,并在AI基础设施集约化发展中扮演战略性物资的角色。”

为了打破“存储墙”瓶颈,2026年的技术路径之一开始从“存储数据”转向“在存储中计算”,即通过将计算与存储深度融合,旨在从根本上消除数据搬运带来的功耗和延迟瓶颈。

广义的存算一体技术根据融合程度的不同,可以分为三个层次:

1.近存计算(NMC):这是最容易实现的形式。它不是在存储单元内部计算,而是通过先进封装技术(如2.5D/3D堆叠)将计算逻辑芯片和存储芯片极度靠近地封装在一起,大幅缩短数据传输路径,从而实现高带宽和低延迟。

2.存内处理(PIM):在这种模式下,少量的计算逻辑单元被集成到存储芯片的IO接口或控制器等外围电路上。比如,三星和SK海力士正在探索的HBM-PIM技术,就是在HBM的每个存储体(Bank)附近放置一个小型处理单元,可以在数据出库前进行一些简单的预处理。

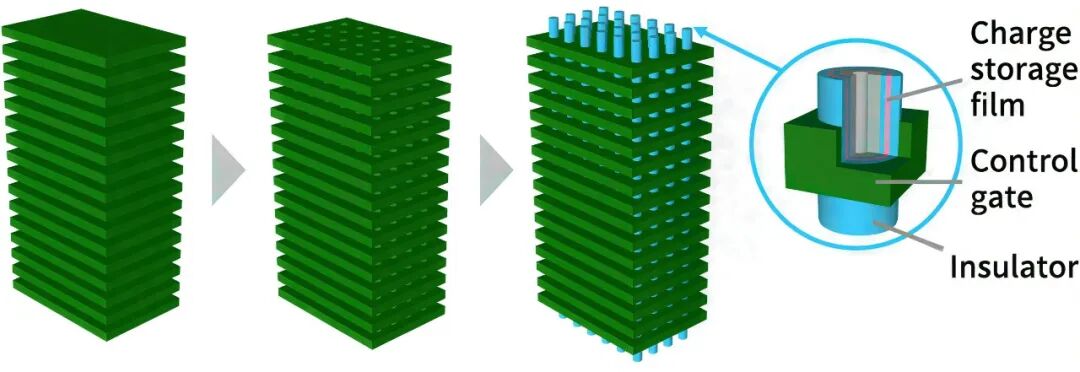

3.存内计算(CIM):这是最彻底的融合形式。计算操作直接在存储单元阵列(Memory Array)内部完成。这通常利用存储单元(如SRAM、ReRAM、闪存)的物理定律来实现。比如,利用ReRAM交叉阵列执行模拟域的向量矩阵乘法,是CIM的典型范例。

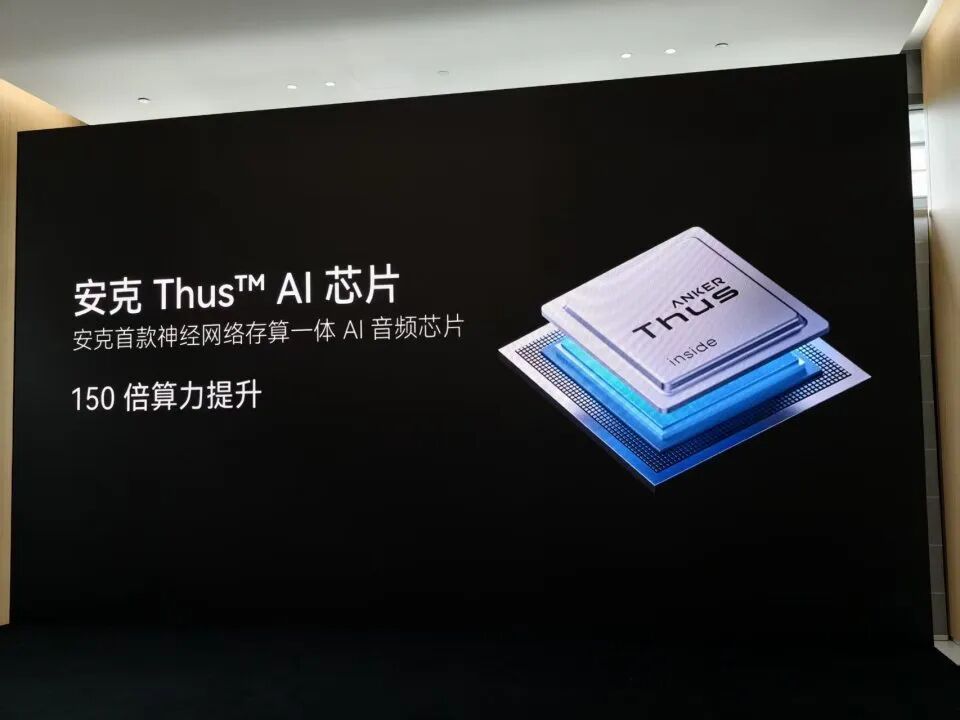

随着技术成熟,一系列存算一体芯片方案开始涌现,它们针对不同的应用场景和技术路径,展示了CIM的巨大潜力。

其中,三星和SK海力士通过在DRAM内部集成逻辑处理单元,改变了传统的冯·诺依曼架构。其核心优势是直接在存储器内部执行大规模并行计算(如AI矩阵运算),可减少内存与CPU/GPU之间80%以上的数据搬运能耗。目前,三星的HBM-PIM已被集成到主流AI加速器中;SK海力士则推出了存内加速器(AiM)解决方案,显著提升了大语言模型(LLM)的推理速度。

而华邦电子的CUBE是近存计算理念的产业化解决方案。它并非一个标准的内存产品,而是一种专为端侧AI设计的定制化高带宽3D DRAM解决方案。CUBE采用创新的3D堆叠架构,通常将客户的系统级芯片(SoC)裸片(Die)置于上层,而将华邦的DRAM Die置于下层,两者通过高密度的TSV进行垂直连接。这种架构相比传统的PCB布线,将SoC与DRAM的距离缩短了几个数量级。

可以说,CUBE作为一种内存解决方案,通过其与SoC的超高带宽接口,为AI加速器提供了一个几乎无延迟的“海量片上缓存”,从而实现了近存计算的效果。这种方案特别适用于对功耗、尺寸和带宽要求极高的端侧AI设备,如AI PC、高端AR/VR眼镜等。

此外,在众多存算一体技术路线中,基于新型NVM的方案备受瞩目。其中,ReRAM因其独特的物理特性,成为业界关注的焦点。在端侧AI中,ReRAM主要有两个应用方向:一是作为高能效的嵌入式非易失性存储,用于存放AI模型的权重参数,实现系统的“即时启动”和低待机功耗;二是被用作存算一体宏单元,直接在存储阵列中执行AI推理计算,大幅降低数据搬运。

目前,一些存储企业正在积极推动ReRAM在边缘AI解决方案中的商业化。芯天下技术负责人钱刚博士就指出,ReRAM具备多电平存储能力,易于扩展至28nm以下先进工艺,并在容量、速度、功耗和面积上展现出综合优势。更重要的是,ReRAM天然适合模拟存算。

他认为,在模拟存算架构中,AI运算中最核心的乘累加(MAC)操作,可以直接利用欧姆定律(电流\=电压×电导)和基尔霍夫电流定律(节点电流总和为零)在物理层面高效完成。存储单元的电导值代表权重,输入的电压代表激活值,输出的电流自然就是乘累加的结果。这种方式避免了数字电路中复杂的逻辑门操作和模数转换(ADC/DAC),从而获得了极高的能效比和计算吞吐率。

目前,芯天下已启动存内计算加速芯片的研发计划,选择了基于ReRAM的模拟存算架构。其路线图清晰:计划于2026年底流片,并在2027年实现量产出货。这款芯片将具备10-50TOPS的算力和超过50TOPS/W的超高能效,并被设计为可无缝集成到现有MCU或DSP系统中的协处理器,通过“算力无感扩容”的理念,为终端设备带来优异的低功耗AI体验。

值得一提的是,随着端侧设备变得越来越复杂,内部不同处理单元(CPU、GPU、NPU、ISP等)之间以及它们与内存之间的高效通信变得至关重要。新型互联标准CXL正为此提供解决方案。尽管CXL目前主要应用于数据中心,但其技术理念对未来的高端边缘计算具有重要的启示和应用潜力。目前,几乎所有主流芯片和系统厂商(Intel、AMD、Arm、三星、美光等)都已加入CXL联盟并推出相关产品。随着技术的成熟和成本的下降,CXL或其简化版本未来有望渗透到高端边缘市场。

结语

AI从云端向端侧的下沉,不仅是应用场景的拓展,更是一场深刻的底层技术革命。在这场革命中,“存储墙”既是最大的障碍,也是最大的机遇。产业界通过主流存储、新兴NVM等技术的协同进化,为端侧AI的初步落地铺平了道路;而存算一体等颠覆性架构的探索,为解决端侧AI面临的终极性能和功耗挑战,描绘了清晰的技术蓝图。

未来的竞争,将不仅是算力的竞争,更是“存力”与“算力”深度融合后,系统级能效与体验的竞争。谁能率先跨越“存储墙”,谁就将掌握端侧AI时代的制胜先机。这场围绕存储的创新竞赛,才刚刚拉开序幕。

评论区

登录后即可参与讨论

立即登录