本文介绍了Chiplet技术对芯片体积减少的作用,及其关键互连技术。

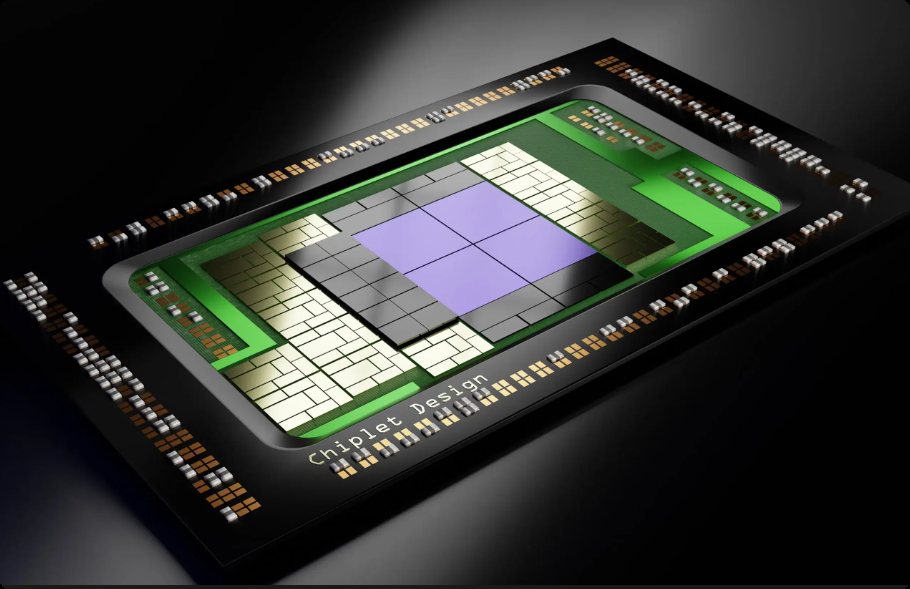

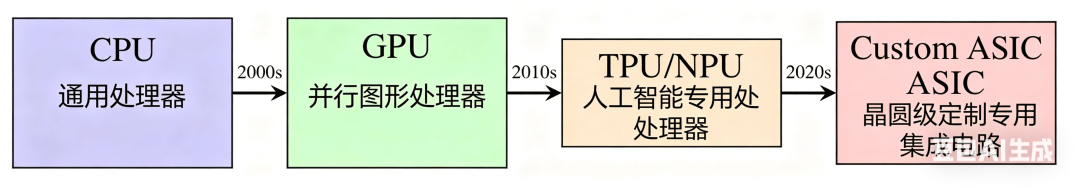

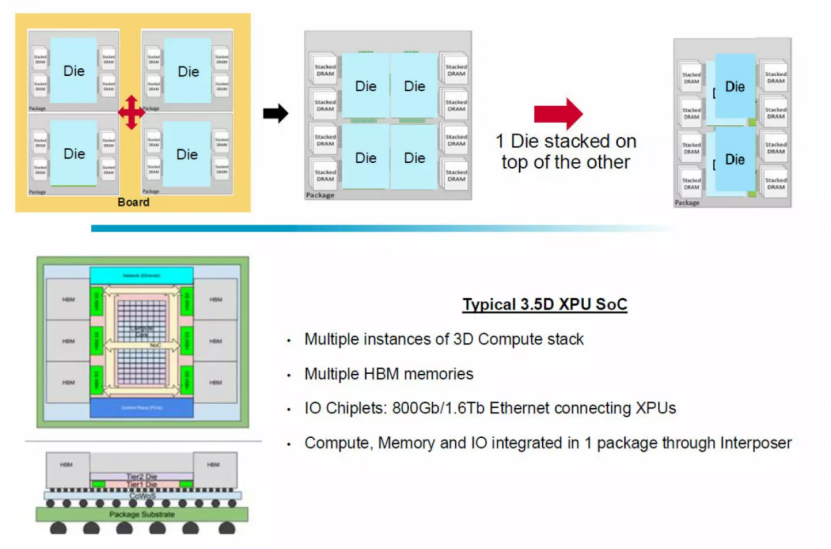

传统芯片设计依靠不断缩小晶体管尺寸来提升性能,但这一路径正面临越来越高的成本和良率压力。Chiplet技术提供了一种新的思路:将原本集成在一颗芯片上的不同功能模块拆分为多个独立的小芯片,再通过先进封装技术将它们重新集成为一个完整的系统。从外部看,它仍然是一颗芯片;但从内部看,它已经是一个由多个芯粒组成的系统。

为什么需要Chiplet

芯片制造中存在一个基本规律:芯片面积越大,良率越低。在相同缺陷密度下,大尺寸芯片更容易因随机缺陷而失效。将一颗大芯片拆分为多个小芯粒,每个芯粒面积更小,良率更容易控制,并且可以在封装前进行测试筛选,这就是“已知良品芯粒”的概念。

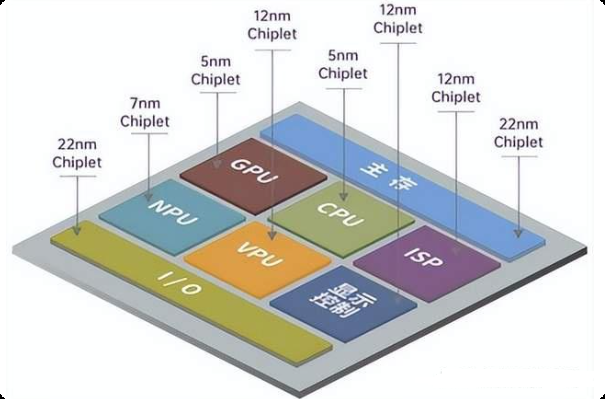

与此同时,一颗高端芯片中不同模块对制程节点的需求并不相同。数字计算核心适合最先进的逻辑工艺,而高速I/O和SerDes更关注模拟特性和信号完整性,SRAM缓存在先进节点上的面积缩放收益并不理想,模拟和射频模块往往需要专用工艺。如果将所有模块强行放在同一先进节点上,不仅成本过高,某些模块的性能也不一定最优。Chiplet允许计算芯粒使用先进逻辑制程,I/O芯粒使用成熟制程,模拟模块使用对应工艺,让每个模块用最合适的工艺。

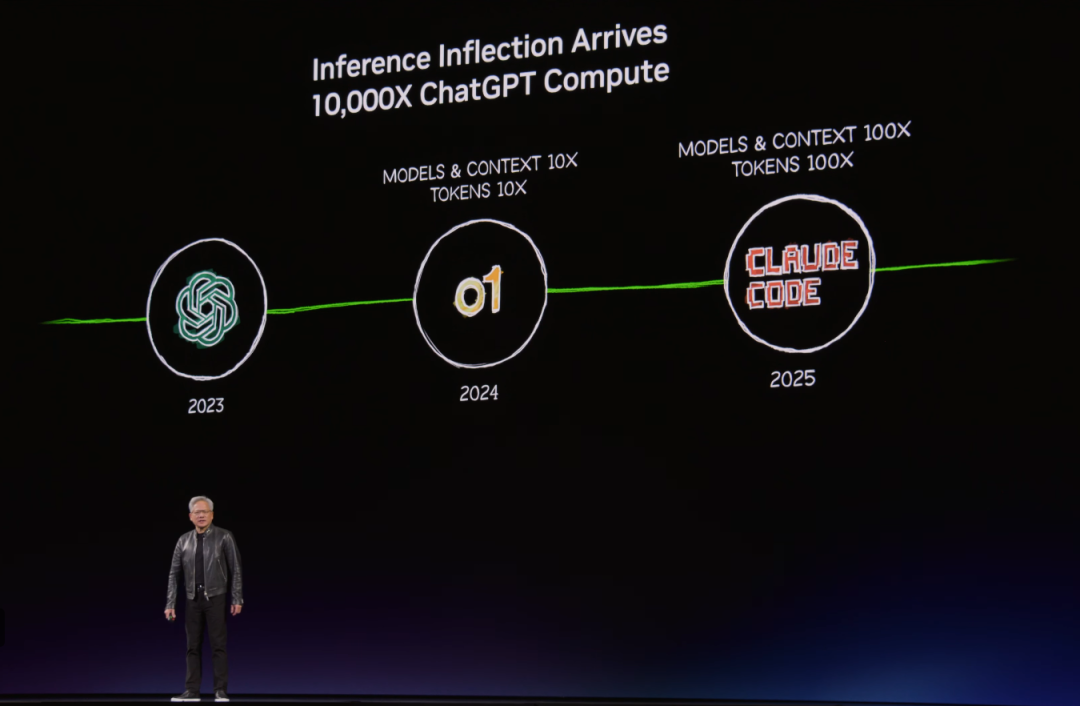

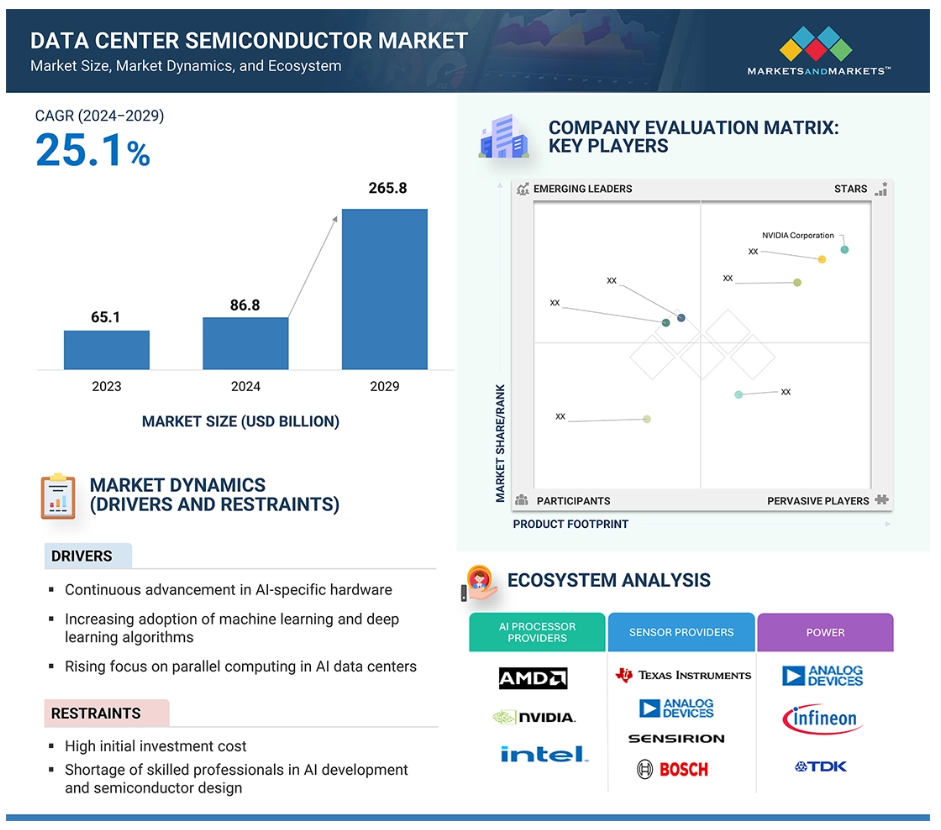

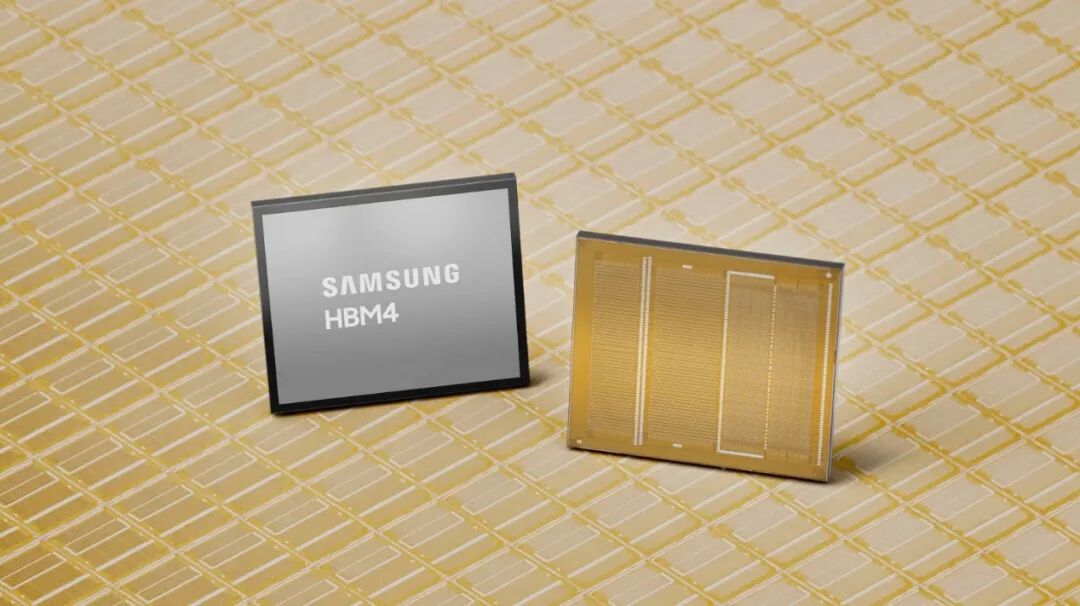

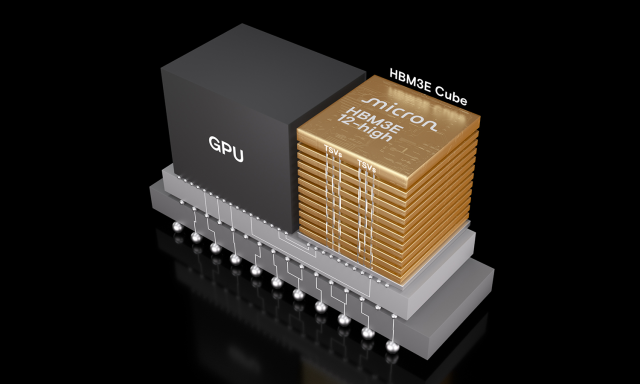

对于AI芯片而言,系统需求已明显超出传统单颗SoC的集成范畴。大模型训练和推理不仅需要大规模矩阵计算能力,还需要TB/s级别的HBM带宽、多颗HBM的并行访问能力、大规模片上互连网络、高速芯片间互连以及高热流密度散热能力。Chiplet允许设计者围绕计算、存储和互连进行模块化布局,将GPU/AI Core、HBM、I/O芯粒通过先进封装平台集成在一起。

实现Chiplet的关键技术

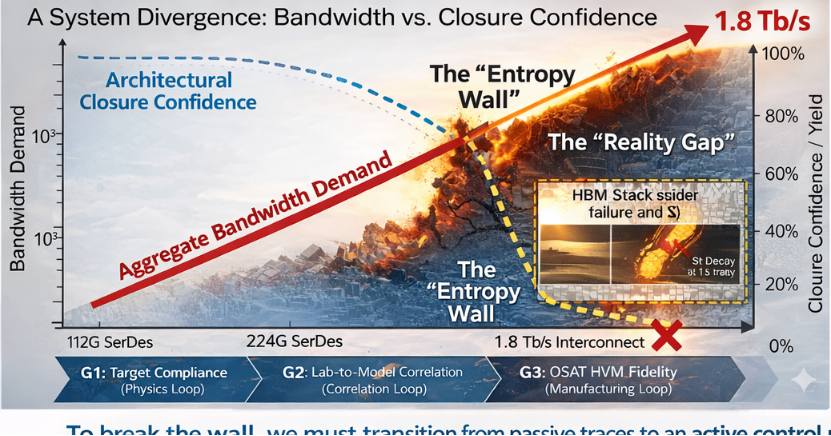

Chiplet能否真正发挥价值,关键在于互连能力。2.5D封装是当前高端AI芯片中最常见的集成方式之一,其基本结构是多个逻辑芯粒和HBM堆栈放置在硅中介层或RDL中介层之上,再通过封装基板连接到系统板。这种方案可以提供高密度、短距离、大带宽的封装内互连,特别适合GPU与HBM之间的宽总线连接。3D封装则通过垂直堆叠进一步缩短互连距离,理论上可以获得更高带宽密度和更低互连功耗,但散热路径受限、堆叠应力复杂、测试和失效定位困难等工程挑战更大。

在互连载体方面,硅中介层的优势是互连密度高、信号完整性好,但面积大、成本高;RDL中介层成本和尺寸扩展性更好,但互连密度通常不如硅中介层。混合键合可以实现更小间距、更高互连密度和更低寄生参数,但对平坦度、表面粗糙度、对准精度等工艺要求极高。

除了封装技术,统一的互联标准同样关键。如果没有统一标准,不同厂商采用私有Die-to-Die互联协议会导致芯粒无法直接协同工作。UCIe是当前最重要的行业联盟标准,针对极短距离通信优化,能够实现高带宽密度和低能耗效率,其延迟可降至纳秒级。包括AMD、Arm、谷歌、微软等科技巨头都已加入UCIe联盟。

Chiplet、HBM和CoWoS是理解现代AI芯片封装的三个关键词。Chiplet是架构拆分方式,HBM是高带宽存储资源,CoWoS是实现高密度集成的封装平台。在高端AI芯片中,常见结构是中间放置GPU或AI计算芯粒,周围布置多颗HBM Stack,底部通过硅中介层实现高密度连接,缩短计算芯粒与HBM的距离,降低单位bit传输能耗。

工程挑战与产业影响

Chiplet并非没有代价。芯片拆分后,原本片上互连的一部分变成了Die-to-Die互连,必须严格控制跨芯粒通信量。如果两个模块之间存在高频、低延迟、强耦合访问,贸然拆分可能导致系统效率下降。电源网络也非常复杂,多个芯粒同时工作时电流瞬态变化大,需要认真处理PDN阻抗、去耦设计、电压跌落等问题。热管理同样关键,多个计算芯粒和HBM在同一封装内会形成复杂的热分布,可能带来局部温度过高、封装翘曲、焊点可靠性降低等问题。

测试策略也需要革新。测试不再是单颗芯片测试,而是包括晶圆级芯粒测试、Known Good Die筛选、芯粒互连测试、封装后系统测试、高速接口测试等。一旦封装后出现失效,要判断问题来自芯粒、互连、封装基板还是热应力,并不容易。Chiplet的测试成本可能占到总成本的25-30%,远高于传统SoC。

从产业链角度看,Chiplet正在改变半导体分工。先进封装的重要性显著提升,封装厂和晶圆厂的协同更加紧密,EDA工具链需要升级以覆盖多芯粒、多封装、多物理场协同问题,测试厂和设备厂的价值随之提升。Chiplet的发展也推动半导体产业向更加专业化的分工模式演变,可能出现专业的芯粒供应商、设计服务商、系统集成商等新业态。

Chiplet的本质是在单片集成接近成本和良率边界之后,通过芯粒化、异构集成和先进封装,实现系统级性能、成本和制造可行性的重新平衡。它解决了算力需求增长与单Die面积限制之间的矛盾、先进制程成本上升与多模块集成需求之间的矛盾。芯片性能提升的路径,正在从单颗芯片做得更大,转向多个芯粒组合得更好。

评论区

登录后即可参与讨论

立即登录