随着高性能计算(HPC)工作负载日益复杂,生成式人工智能(AI)正逐步集成到现代系统中,从而推动了对先进内存解决方案的需求。为了满足这些不断变化的需求,业界正在开发下一代内存架构,旨在最大化带宽、最小化延迟并提高能效。

DRAM、LPDDR和专用内存解决方案的技术进步正在重新定义计算性能,其中AI优化内存发挥着关键作用,有助于提升效率和可扩展性。本文将探讨内存技术的最新突破,以及AI应用对内存设计日益增长的影响。

先进内存架构

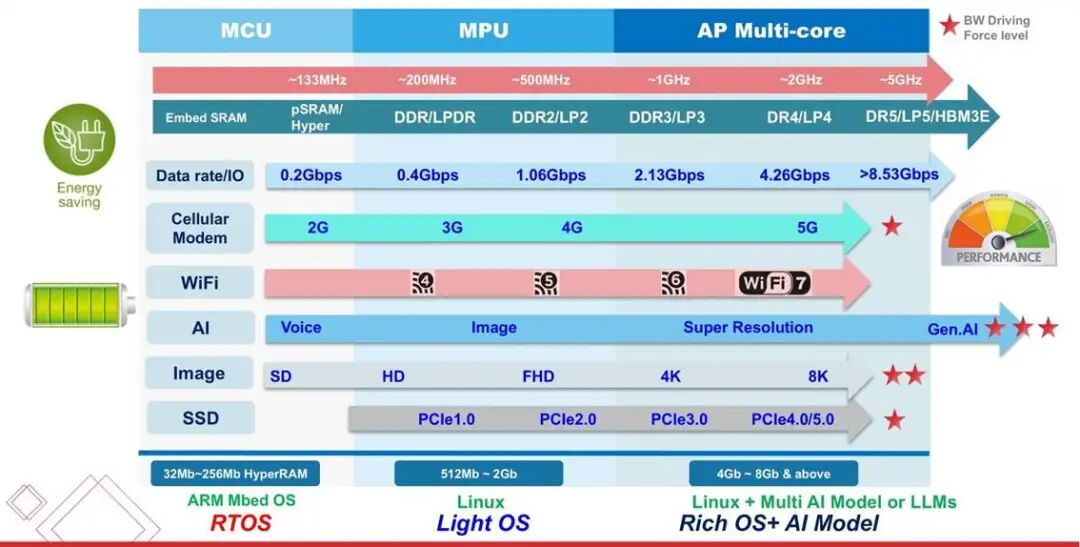

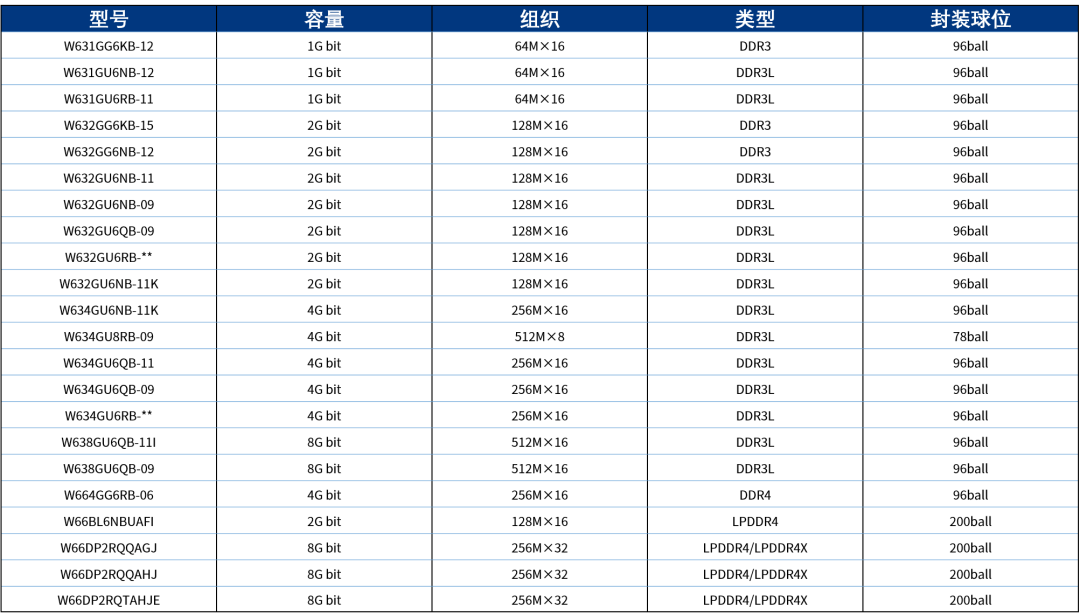

内存技术正在不断演进,以满足AI、AIoT和5G系统严苛的性能要求。随着DDR5和HBM3E的广泛应用,业界正经历一场范式转变,它们提供了更高的带宽和更佳的能效(图1)。

DDR5的单引脚数据速率高达6.4Gbps,单模块速度可达51.2GB/s,性能几乎是DDR4的两倍;同时,电压从1.2V降至1.1V,进一步提高了能效。HBM3E进一步扩展了带宽,单堆栈速度超过1.2TB/s,使其成为数据密集型AI训练模型的理想选择。然而,由于其功耗过高,并不适用于移动和边缘部署。

图1:从基于MCU的嵌入式系统到服务于高端应用的AI加速器的内存扩展历程。(来源:华邦电子)

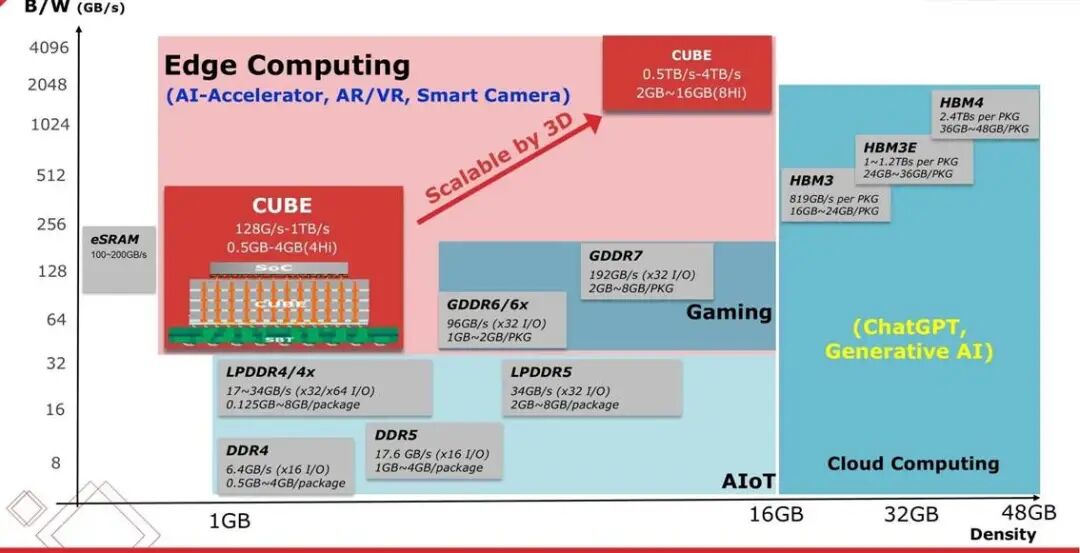

LPDDR6预计在2026年内实现超过150GB/s的吞吐量。低功耗DRAM正朝着更高吞吐量和能效的方向发展,以应对AI智能手机和嵌入式AI加速器面临的挑战。华邦电子正积极开发基于其CUBE内存平台的、针对功耗敏感型应用优化的低容量DDR5和LPDDR4解决方案。CUBE内存平台实现了超过1TB/s的带宽,并显著降低了散热需求。

基于单一掩模尺寸,CUBE内存的单组容量预计可扩展至8GB甚至更高。例如,采用4层晶圆堆叠(4Hi WoW)技术,可实现超过70GB的密度和40TB/s的带宽。因此,CUBE有望成为AI驱动的边缘计算领域中传统DRAM架构的可行替代方案。

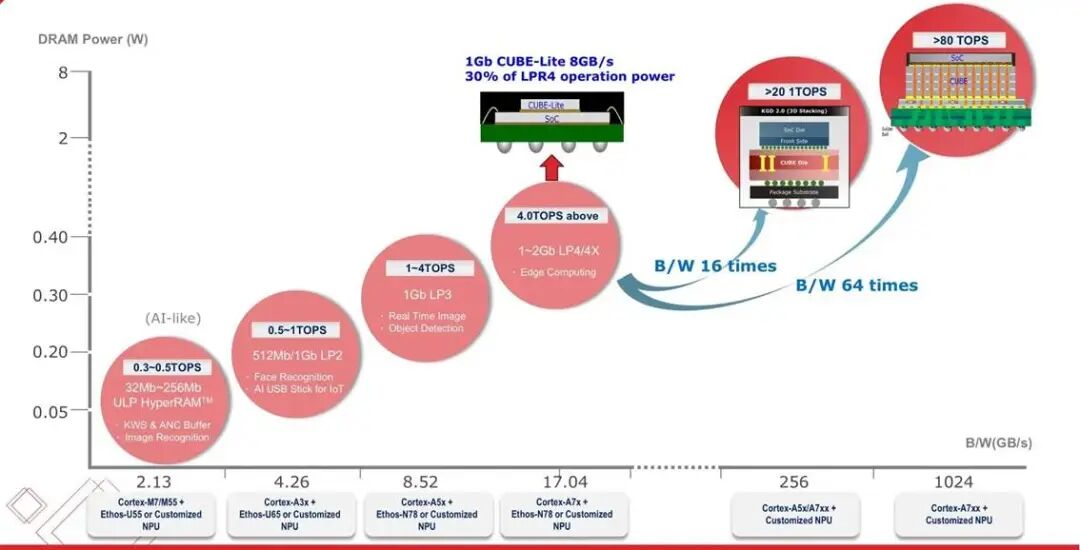

此外,CUBE子系列(称为CUBE-Lite)提供8至16GB/s的带宽(相当于LPDDR4x x16/x32),而功耗仅为LPDDR4x的30%(图2)。由于无需LPDDR4 PHY,系统级芯片(SoC)只需集成CUBE-Lite控制器即可实现与全速LPDDR4x相当的带宽性能。这不仅省去了高昂的PHY授权费用,还允许使用成熟的工艺节点(如28纳米甚至40纳米),从而达到12纳米节点的性能水平。

基于此,仅采用CUBE-Lite控制器且不包含LPDDR4 PHY的SoC,不仅能显著缩小芯片尺寸,还能大幅提升系统能效。这种架构专为电池供电设备设计,尤其适用于集成NPU、MPU或MCU的AI SoC以及TinyML终端设备。在此类系统中,通过运行Micro Linux操作系统并加载AI模型,可高效驱动低功耗AI图像信号处理器(ISP),广泛应用于IP摄像头、AI眼镜和可穿戴设备等场景,有效实现系统功耗优化与芯片面积缩减的双重目标。

图2:内存带宽随DRAM功耗的变化情况。(来源:华邦电子)

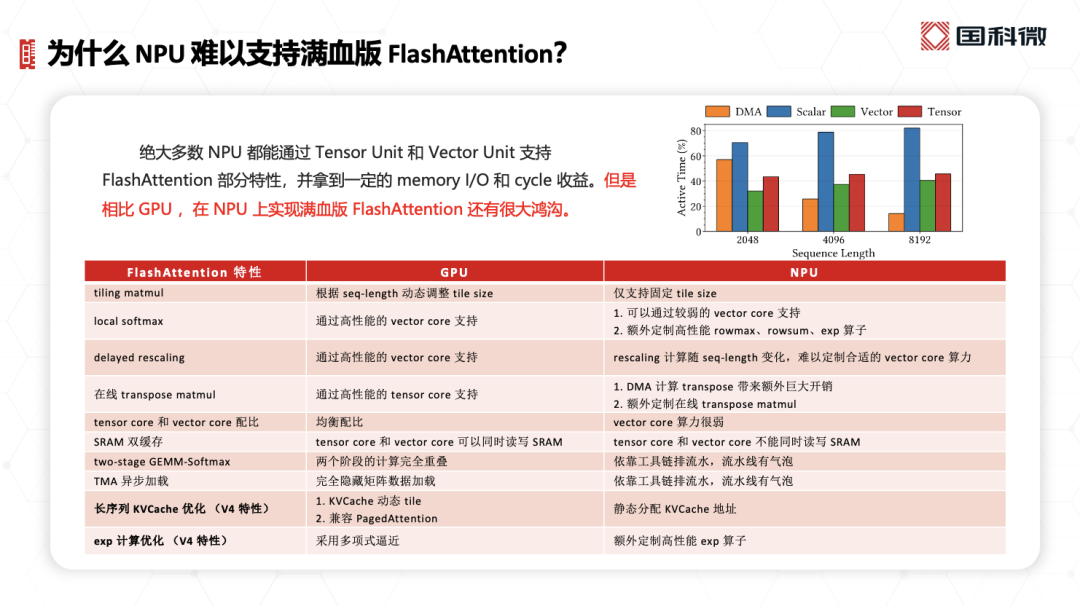

生成式AI部署中的内存瓶颈

生成式AI模型的指数级增长对内存带宽和延迟提出了前所未有的要求。AI工作负载,尤其是那些依赖于Transformer架构的工作负载,需要大量的计算吞吐量和高速数据检索。

例如,在INT8模式下部署LLaMA2 7B至少需要7GB的DRAM,或在INT4模式下需要3.5GB,这凸显了传统移动内存容量的局限性。目前采用LPDDR5(带宽为68GB/s)的AI智能手机面临着严重的瓶颈,因此需要过渡到LPDDR6。然而,在LPDDR6商业化之前,需要一些过渡解决方案来弥合带宽差距。

在系统层面,机器人、自动驾驶汽车和智能传感器等AI边缘应用对电源效率和散热提出了额外要求。虽然JEDEC标准正在不断发展,朝着DDR6和HBM4方向发展以提高带宽利用率,但定制内存架构提供了可扩展的高性能替代方案,能够满足AI SoC的要求。

散热管理和能效限制

在终端设备上部署大规模AI模型会带来重大的散热管理和能效挑战。AI驱动的工作负载本身就会消耗大量电力,产生过多热量,从而降低系统稳定性和性能。

设备端内存扩展:移动设备必须集成更高容量的内存解决方案,以最大限度地减少对云端AI处理的依赖并降低延迟。传统的DRAM扩展已接近物理极限,因此需要集成高带宽和低功耗内存的混合架构。

用于AI SoC的HBM3E与CUBE:虽然HBM3E可以实现高吞吐量,但其每个堆栈的功耗超过30W,使其不适用于移动和边缘应用。在这种情况下,CUBE等内存解决方案可以作为替代的末级缓存(LLC),在保持高速数据访问的同时,减少对片上SRAM的依赖。向7纳米以下逻辑工艺的转变加剧了SRAM扩展的限制,凸显了对新型缓存解决方案的需求。

热优化策略:由于AI处理产生的热负载超过每芯片15W,因此有效的电源分配和散热机制至关重要。采用优化刷新周期和基于TSV封装技术的定制DRAM解决方案,有助于在紧凑的外形尺寸下实现高效的AI执行。

DDR5和DDR6:加速AI计算性能

DDR5和DDR6的演进是AI系统架构的一个重要转折点,可提供更高的内存带宽、更低的延迟和更强的可扩展性。

DDR5采用8组内存架构和片上纠错码(ECC),提供卓越的数据完整性和效率,使其非常适合AI增强型PC和高性能笔记本电脑。DDR5的有效峰值传输速率为每模块51.2GB/s,可实现实时AI推理、无缝多任务处理和高速数据处理。

DDR6仍在开发中,预计每个模块的带宽将超过200GB/s,功耗将降低20%,同时优化AI加速器支持,进一步将AI计算能力推向新的极限(图3)。

图3:CUBE——利用硅通孔(TSV)互连技术融合高带宽内存特性与低功耗表现的AI优化内存解决方案。(来源:华邦电子)

AI驱动的工作负载、性能扩展的限制以及对节能内存解决方案的需求,正在共同推动内存市场的转型。生成式AI持续加速了对低延迟、高带宽内存架构的需求,从而推动DRAM和定制内存解决方案的创新。

随着AI模型日益复杂,对优化、节能的内存架构的需求将变得愈发关键。在此,技术创新将确保尖端AI内存解决方案的商业化,弥合高性能计算与可持续、可扩展内存设备之间的鸿沟。

评论区

登录后即可参与讨论

立即登录