二氧化硅(SiO₂)和氮化硅(Si₃N₄)是最常用的两种介电材料, 本文将详细介绍氮化硅在不同温度区间的沉积方法。

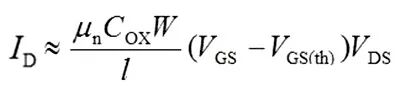

介电材料作为绝缘层与光学薄膜,在半导体微芯片制造领域应用广泛。其中二氧化硅(SiO₂)和氮化硅(Si₃N₄)是最常用的两种介电材料,Si-SiO₂界面的优异特性,让该结构成为金属-氧化物-半导体场效应晶体管(MOSFET)的核心基石。本文将详细介绍Si₃N₄在不同温度区间的沉积方法。

低压化学气相沉积(LPCVD)

Si₃N₄薄膜的沉积方法主要有两种:低压化学气相沉积(LPCVD)和 PECVD。LPCVD 的工艺压力通常设置为 0.15-2 托,而热氧化工艺在 1 标准大气压下进行。此外半导体制程中还有高压工艺,如高压氧化(HIPOX)工艺,其工艺压力为 10-25 标准大气压,核心特点是能提高薄膜生长速率,广泛应用于 LOCOS 和 STI 技术。

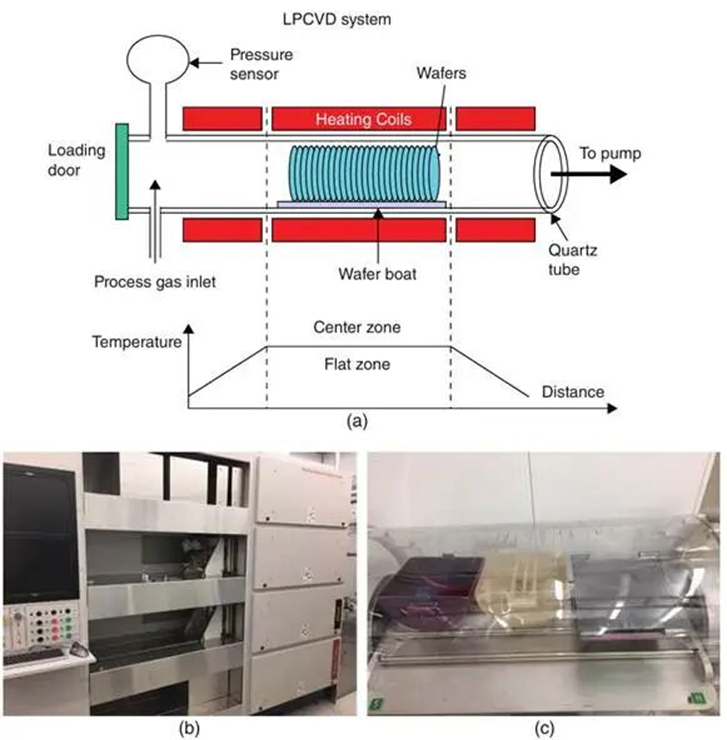

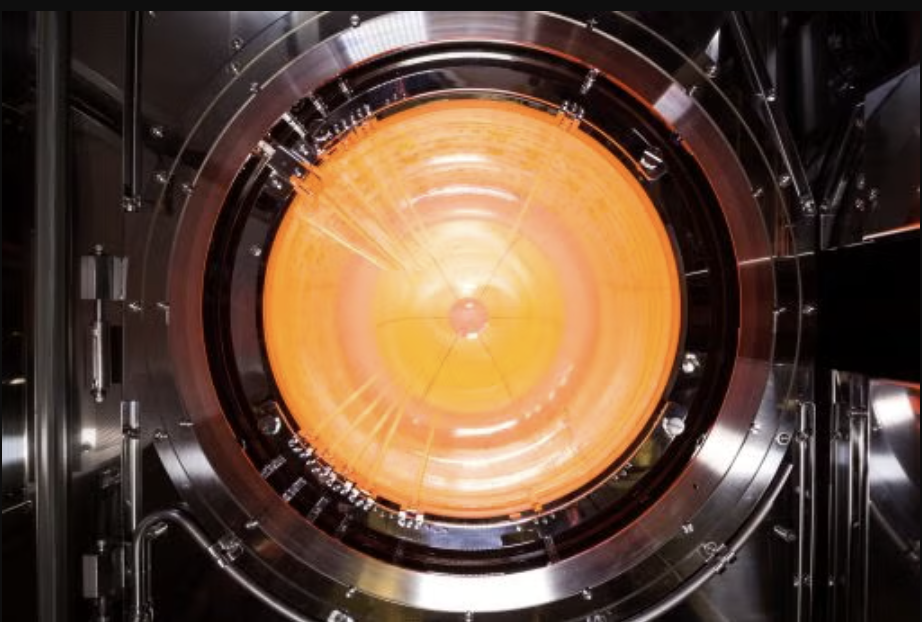

LPCVD 设备的基本结构与热氧化炉类似,核心组件为石英管和加热电阻丝,二者的核心区别在于,热氧化炉无真空泵组件,而 LPCVD 设备连接有真空泵(见图1)。设备示意图中设有三个加热区,硅片放入中间加热区进行工艺处理,热氧化炉也采用相同的多加热区设计。图中的石英舟放置在推车上进行防护,舟体材料可选用石英或石墨。

图 1 低压化学气相沉积(LPCVD)系统相关示意图及照片(a)结构示意图:石英管外有加热线圈,晶圆放置在石英舟中并置于石英管中心加热区,工艺气体从一端通入,另一端连接真空泵,通过压力传感器监测腔室压力;(b)LPCVD 设备实物照片;(c)石英舟和石墨舟:用于装载晶圆进行沉积工艺。

LTO 工艺所用设备与 LPCVD 设备相同,实际生产中,一台 LPCVD 设备可配备多根不同的石英管,用于沉积不同类型的薄膜。栅极用多晶硅薄膜,便是通过 LPCVD 设备制备——在 600-700℃温度范围内,采用硅烷法沉积SiO₂时,若体系中无氧气,便会在器件表面沉积多晶硅薄膜;PECVD 工艺中若去除氧源,也可沉积硅薄膜,受限于较低的工艺温度,PECVD 沉积的硅薄膜为非晶硅。多晶硅与非晶硅的核心区别在于,多晶硅的晶粒尺寸远大于非晶硅。

沉积Si₃N₄薄膜的常用反应气体为二氯硅烷(DCS,化学式为 H₂SiCl₂)和氨气(NH₃)。其中 DCS 为反应提供硅原子,选用氨气而非纯氮气作为氮源的原因是,氮气的分子键能最大,化学键难以断裂,PECVD 沉积Si₃N₄薄膜时也采用氨气作为氮源。在 750-850℃温度范围内,两种气体发生如下化学反应:3H₂SiCl₂(g) + 4NH₃(g) → Si₃N₄(s) + 6HCl (g) + 6H₂(g)。

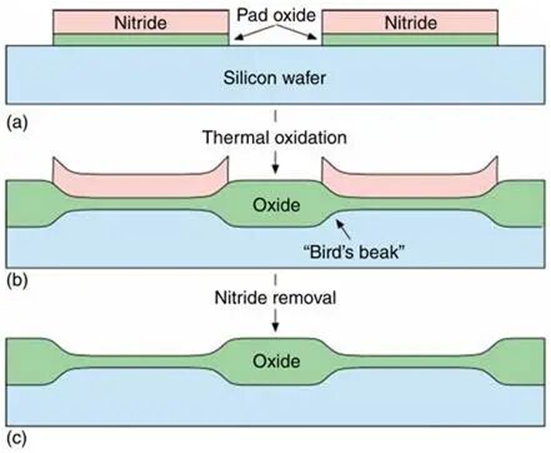

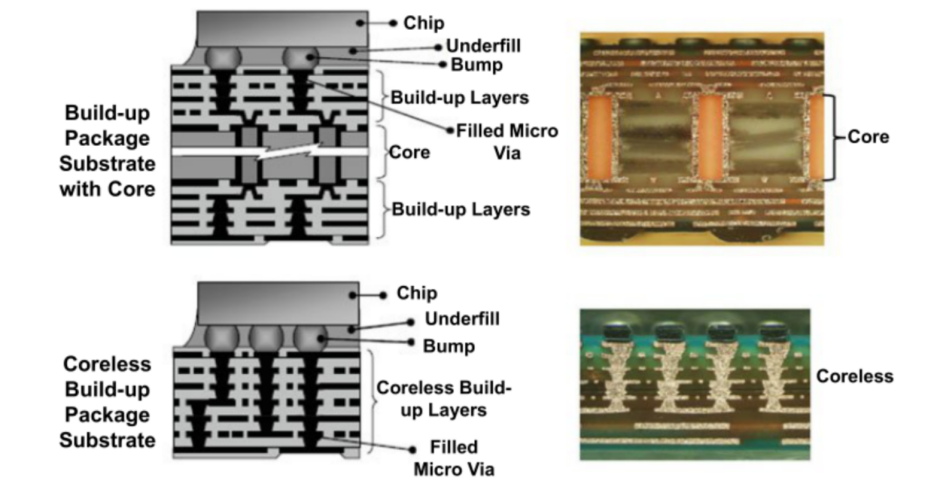

LPCVD 制备的Si₃N₄薄膜结构极为致密,其中一个重要应用是作为 LOCOS 工艺中的掩模层。LOCOS 是传统的集成电路隔离技术(见图2),该工艺的第一步是在硅衬底上热生长一层薄SiO₂(称为垫氧化层),再通过 LPCVD 在该氧化层上沉积Si₃N₄薄膜;随后利用光刻工艺在薄膜上制作图形,通过干法刻蚀在图形开口处刻蚀至硅表面;最后将硅片放入高压氧化炉进行热氧化。

致密的Si₃N₄薄膜作为阻挡掩模,能有效阻止氧或水蒸气的扩散,因此氧化反应仅发生在无Si₃N₄薄膜覆盖的开口处。

图 2局部氧化隔离(LOCOS)工艺流程示意图(a)刻蚀Si₃N₄(Si₃N₄)和垫氧层(pad-oxide)直至硅表面,形成开口;(b)通过开口进行热氧化,生成氧化层,Si₃N₄层作为阻挡掩模抑制氧气/水蒸气扩散,氧化过程中产生 “鸟嘴”(Bird’s beak)现象;(c)去除Si₃N₄薄膜,完成隔离结构制备。

图中的“鸟嘴”结构是LOCOS 技术的固有问题,由工艺中的横向氧化导致,因此该技术仅适用于特征尺寸大于0.25微米的器件。通过热氮化法生长Si₃N₄薄膜的速率极慢,且该工艺具有自限制性。这是因为Si₃N₄薄膜的致密度极高,氮气与硅反应生成Si₃N₄薄膜后,会阻挡氮气继续向硅衬底扩散,从而使Si₃N₄的生长停止。通过硅与氨气的热氮化反应,制备的薄膜厚度仅为 3-4 纳米,受此限制,该工艺仅用于制造部分特殊器件。硅与氨气的热氮化反应如下:3Si (s) + 4NH₃(g) → Si₃N₄(s) + 6H₂(g)。

Si₃N₄的等离子体增强化学气相沉积(PECVD)工艺

Si₃N₄的PECVD沉积设备与SiO₂的 PECVD 沉积设备基本相同,但存在一些细微差异:

1. 通入工艺腔室的反应气体不同:SiO₂沉积使用稀释后的硅烷和笑气,Si₃N₄沉积则使用稀释后的硅烷和氨气;

2. 电源配置不同:SiO₂沉积设备通常仅需一套电源(13.56兆赫兹,即高频电源),而Si₃N₄沉积设备配备两套电源,一套为13.56兆赫兹的高频电源,另一套为300-400千赫兹(kHz)的低频电源。

图3 沉积Si₃N₄薄膜的PECVD 设备照片。可通过切换通入的工艺气体(稀释硅烷+氨气或稀释硅烷+一氧化二氮),实现 Si₃N₄或SiO₂薄膜的沉积。

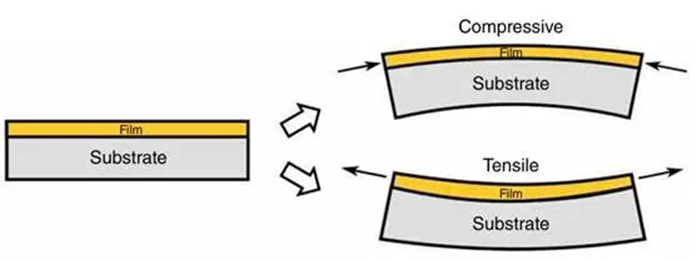

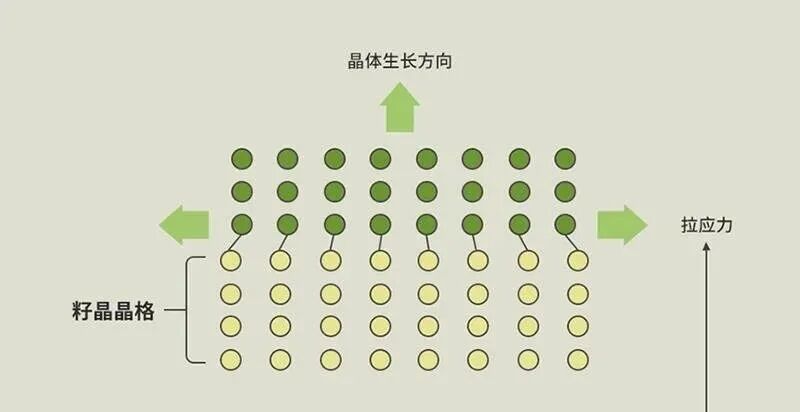

在硅衬底上,采用高频电源沉积的Si₃N₄薄膜表现为拉应力,会导致硅片凸起;采用低频电源沉积的Si₃N₄薄膜表现为压应力,会导致硅片凹陷(见图 4)。若同时使用高频和低频电源,可制备出低应力的Si₃N₄薄膜。

图 4 不同射频电源沉积的 Si₃N₄薄膜对硅晶圆形态的影响(a)采用高频(HF,13.56 MHz)电源沉积的 Si₃N₄薄膜呈拉伸应力,导致硅晶圆凸起;(b)采用低频(LF,300–400 kHz)电源沉积的 Si₃N₄薄膜呈压缩应力,导致硅晶圆凹陷。

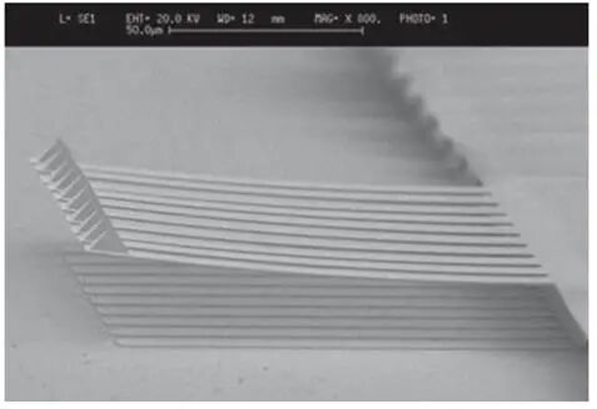

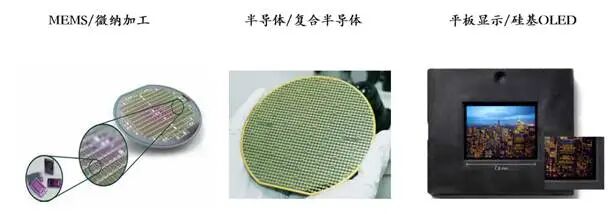

Si₃N₄薄膜的应力特性在器件制造中有着诸多应用,尤其是微机电系统(MEMS)领域。例如利用具有拉应力的Si₃N₄薄膜制作悬臂梁,前文提到的微米级变压器也采用了Si₃N₄薄膜的应力调控技术。

图 5 硅氮化膜(Si₃N₄)拉伸应力悬臂梁的SEM照,利用Si₃N₄薄膜的拉伸应力实现悬臂梁结构

在硅表面沉积压应力薄膜时,衬底与薄膜的结合面更易贴合;沉积拉应力薄膜时,衬底与薄膜的结合面则易出现分离。因此,若将Si₃N₄薄膜用作集成电路的最终钝化膜,应选用压应力薄膜,其对应的器件可靠性高于拉应力薄膜。

上述工艺中使用的气体多为可燃气体(如DCS和硅烷均为可燃气体,易分解析出氢气),且DCS为有毒气体(易分解析出氯气),这类可燃有毒气体被统称为危险气体。使用危险气体时,真空泵从设备中抽出的废气,必须先经过可控分解氧化(CDO)设备和废气处理设备处理后,才能排放到大气中。含氟气体(CF₄、CHF₃、SF₆)不可燃且无毒,可直接进入废气处理设备(洗涤器),无需经过 CDO 设备处理。

图 6 受控分解氧化装置(CDO)(a)和废气洗涤器(scrubber)(b)(a)用于对工艺废气进行受控氧化分解处理;(b)用于去除废气中的有害物质,避免环境污染。

原子层沉积技术

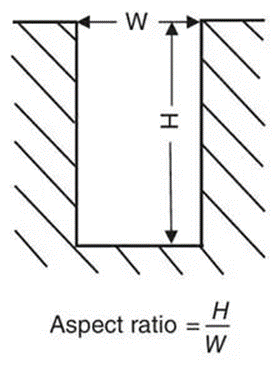

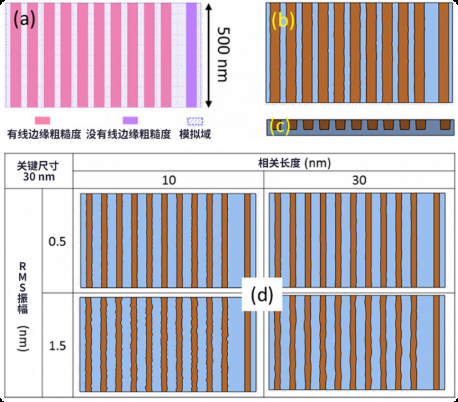

前文讨论的薄膜沉积技术已广泛应用于微芯片制造,但随着器件特征尺寸的不断缩小,这些技术面临两个难以解决的共性问题:薄膜沉积的均匀性控制,以及在高深宽比结构上实现保形层沉积。在半导体制造中,深宽比主要指刻蚀结构的高度与宽度之比。

图7 深宽比示意图。深宽比(Aspect ratio)定义为刻蚀结构的高度(H)与宽度(W)之比(H/W)

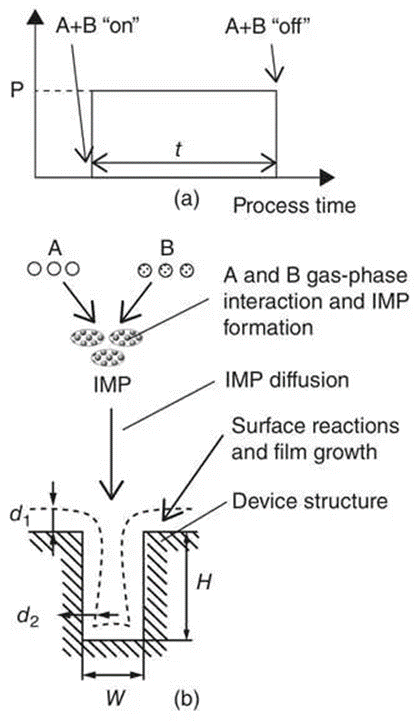

原子层沉积(ALD)是解决这两个问题的有效技术,本文将以 CVD 系统为参照,介绍 ALD 系统的相关特性。常规 CVD 工艺在流式反应器中进行,反应物同时连续注入反应器,反应副产物则被连续去除,其主要特征参数包括沉积温度(T,℃)、沉积压力(P,毫托)、沉积时间(t,分钟或秒)和气体流量(标准立方厘米每分钟,sccm,后续介绍)。

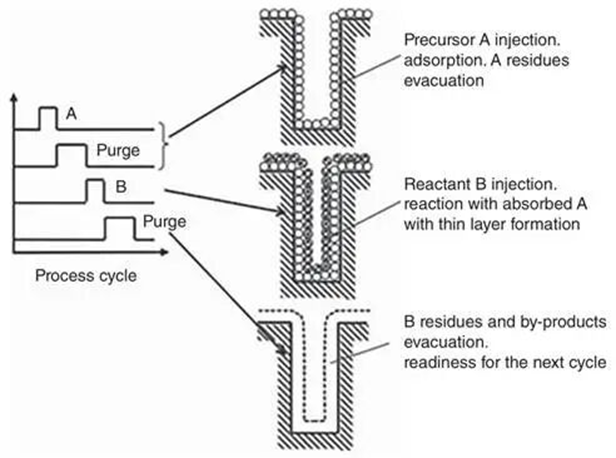

而 ALD 技术的工艺实现方式和特征与 CVD 完全不同,ALD 工艺以循环方式进行,前驱体和其他反应物通过惰性气体(主要为氮气)分隔,依次脉冲注入反应腔。ALD 系统主要分为两种类型:热激活原子层沉积(TA-ALD)和等离子体增强原子层沉积(PE-ALD)。

图8 化学气相沉积(CVD)过程示意图(a)反应气体 A 和 B 持续通入反应腔室(“on” 状态),反应后停止通入(“off” 状态);(b)气体 A 和 B 在气相中反应生成中间产物(IMP),中间产物扩散至器件结构表面,通过表面反应生长薄膜,d₁为结构顶部薄膜厚度,d₂为结构底部薄膜厚度。

图8为反应物A和B的CVD工艺示意图,图9为前驱体A和反应物B的循环工艺示意图(代表TA-ALD工艺)。对于PE-ALD工艺,等离子体放电通常在反应物脉冲开始一段时间后开启,在脉冲结束时关闭。

图9 原子层沉积(ALD)循环过程示意图。前驱体 A 注入并吸附于器件结构表面,吹扫去除残留前驱体 A;反应物 B 注入并与吸附的前驱体 A 发生反应,形成薄层薄膜;再次吹扫去除残留反应物 B 及反应副产物,完成一个沉积循环,准备进入下一轮循环,实现层状沉积。

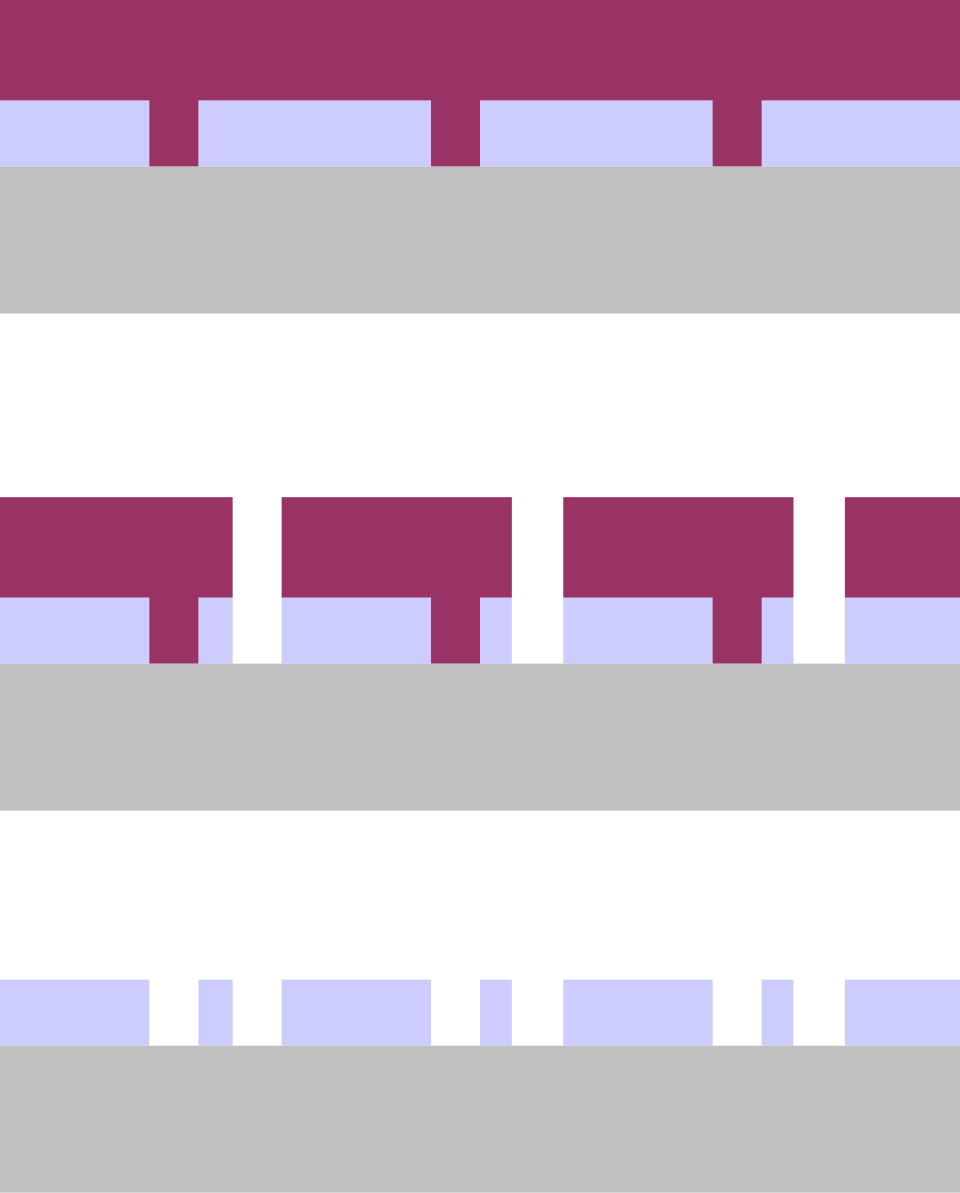

台阶覆盖率(即薄膜保形性)可用台阶(或间隙)底部的薄膜厚度与顶部的薄膜厚度之比(d₂/d₁,%)表示。受 CVD 工艺原理及工艺条件限制,其制备的薄膜保形性较差,且随着薄膜厚度增加,刻蚀结构的顶部开口会逐渐闭合,导致薄膜内部形成空隙。

与 CVD 不同,ALD 工艺完全避免了反应物在气相中的相互作用,以及中间产物(IMP)的形成和扩散,所有工艺过程均高度局限于衬底表面,其核心优势是实现原子级的逐层沉积(因此称为原子层沉积)。得益于自限制性的表面化学反应,ALD工艺能实现薄膜的均匀沉积,且作为高度表面限制的工艺,ALD具有优异的薄膜保形性,适合在高深宽比结构上进行薄膜沉积。

ALD 工艺所用的硅前驱体有多种,常用的一种是双(二乙胺基)硅烷(BDEAS,化学式为 SiH₂[N (C₂H₅)₂]₂)。沉积SiO₂的反应物通常是臭氧发生器产生的臭氧,沉积Si₃N₄的反应物通常是氨气(NH₃)。ALD 工艺的温度通常在 200-400℃范围内,通过该技术可制备单层薄膜和高保形性的SiO₂、Si₃N₄薄膜,但沉积速率相对较慢。

图10 热激活原子层沉积(TA-ALD)设备照片。顶部为反应腔室,前驱体钢瓶外包裹加热套,用于控制前驱体状态。

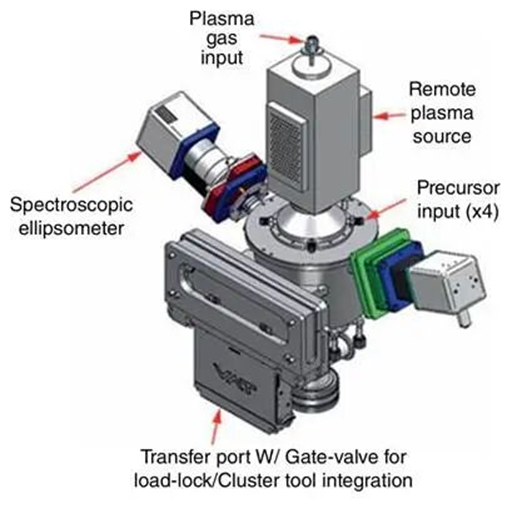

图 10为TA-ALD设备照片,图11为 PE-ALD设备示意图,其中光谱椭圆偏振仪用于原位测量薄膜厚度,真空阀门(VAT 阀门)则广泛应用于各类半导体制造设备中。

图 11等离子体增强原子层沉积(PE-ALD)反应器示意图。包含等离子体气体输入口、远程等离子体源、4 个前驱体输入口、光谱椭偏仪(用于原位监测薄膜厚度)、装载锁 / 集群工具集成接口及带门阀的传输端口。

评论区

登录后即可参与讨论

立即登录