刻蚀形貌由什么决定的?

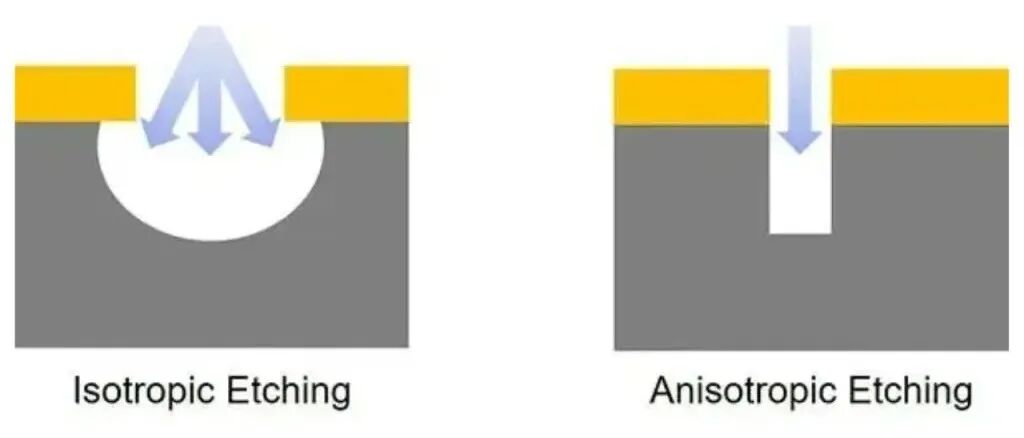

本文主要介绍了刻蚀形貌由什么决定的。 在芯片制造的纳米雕刻中,刻蚀工艺不仅仅是“挖掉”不需要的材料,更要挖出特定形状的轮廓。这些轮廓——是笔直的矩形,还是上宽下窄的正梯形,或是上窄下宽的倒梯形——直接决定了后续金属填充的质量、晶体管的性能,甚至整个芯片的良率。那么,工程师们是如何在纳米尺度上操控这些形状的呢? 一、刻蚀形貌的三种基本形态 在刻蚀工艺中,形貌通常分为三种典型形态: 矩形(各向异性)

纳米网制造工艺频道 — 提供制造工艺领域最新资讯、技术文章和行业动态。

本文主要介绍了刻蚀形貌由什么决定的。 在芯片制造的纳米雕刻中,刻蚀工艺不仅仅是“挖掉”不需要的材料,更要挖出特定形状的轮廓。这些轮廓——是笔直的矩形,还是上宽下窄的正梯形,或是上窄下宽的倒梯形——直接决定了后续金属填充的质量、晶体管的性能,甚至整个芯片的良率。那么,工程师们是如何在纳米尺度上操控这些形状的呢? 一、刻蚀形貌的三种基本形态 在刻蚀工艺中,形貌通常分为三种典型形态: 矩形(各向异性)

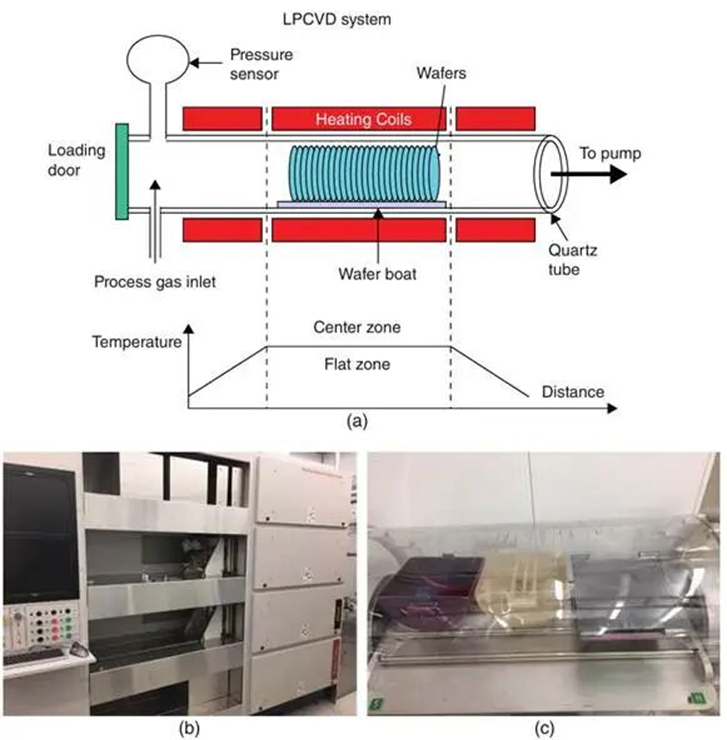

本文主要介绍单晶硅湿法刻蚀用什么做掩膜。 在单晶硅的湿法刻蚀中,选择何种材料作为掩膜(Mask),严格取决于所使用的刻蚀液的化学成分以及刻蚀的深度与时间。 产线中最常用的掩膜材料分为硬掩膜(Hard Mask)和金属掩膜,具体分类和应用条件如下: 1. 氮化硅 :适用性最广的深层刻蚀掩膜 适用刻蚀液: 碱性刻蚀液(如 KOH、TMAH)和酸性刻蚀液(如 HNA)。 通过低压化学气相沉积(LPCV

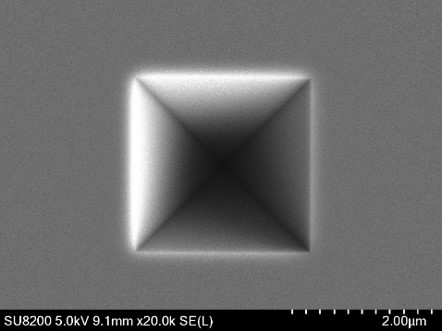

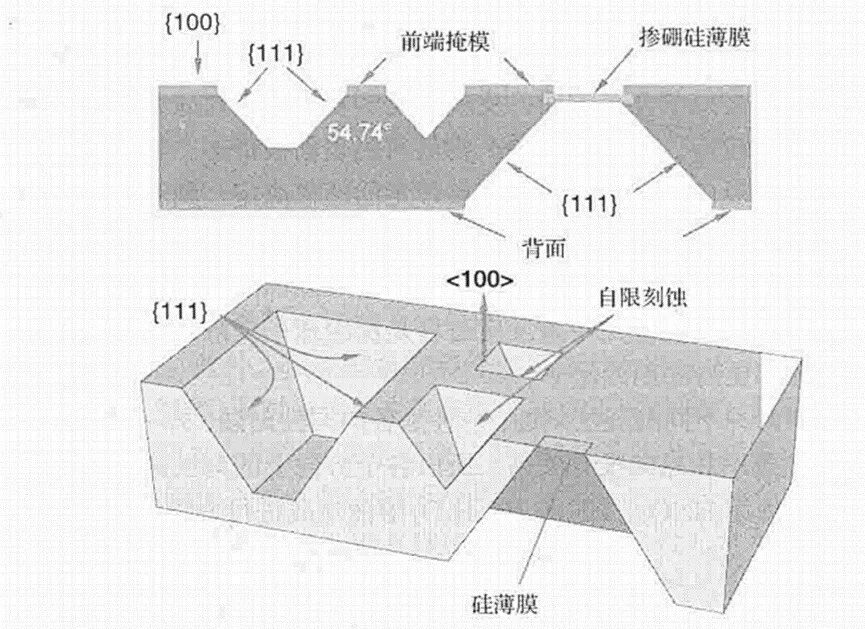

本文将介绍体微机械、各向异性刻蚀与表面微机械的工艺图谱。 体微机械工艺 体微机械工艺作为MEMS制造中历史最为悠久的微机械工艺类型,其核心在于通过选择性刻蚀去除部分衬底以形成所需微结构,该工艺深度融合了传统微电子工艺与高度专业化的微机械加工能力。在湿法化学体微加工领域,其凭借高刻蚀速率与高选择比的优势长期占据工业应用主导地位,刻蚀过程通过光刻胶图案转印后,将衬底浸入刻蚀溶液实现未保护区域的去除,其

据韩媒thelec最新报道,三星已成功生产出基于10纳米以下工艺的DRAM工作芯片(working die),这标志着其在克服存储器制造工艺的物理微缩极限方面,迈出了商业化应用的关键一步。 在DRAM行业的技术命名体系中,10纳米级制程节点已从1x、1y、1z演进至1d。而此次三星实现突破的“10a”节点,是首个实际线宽低于10纳米的工艺,其电路线宽估计在9.5至9.7纳米之间。 “工作芯片”是指

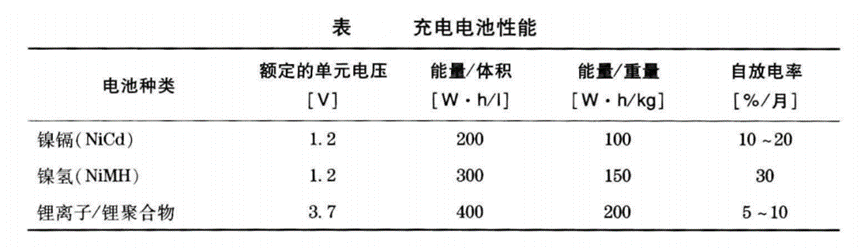

本文将介绍CMOS功耗优化领域。 CMOS设计 低功耗CMOS集成电路设计作为半导体领域的核心研究方向,其发展脉络与行业需求紧密交织,自20世纪70年代CMOS技术初步应用以来,历经半个世纪的演进,已从早期的特定场景应用拓展为全行业普适性设计理念。 20世纪80年代中期,随着VLSI技术对高集成度与低功耗的双重需求凸显,CMOS凭借其静态功耗低、工艺兼容性强的优势,逐步取代nMOS成为主流工艺,这

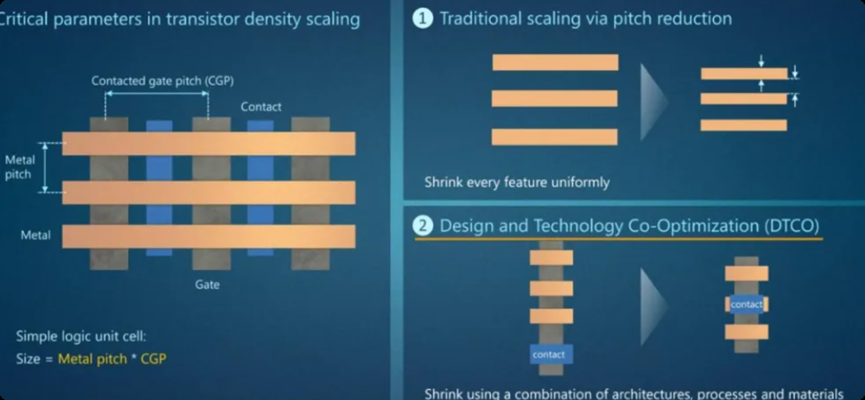

本文将详细介绍DTCO(设计-工艺协同优化)与STCO(系统-工艺协同优化)。 随着半导体工艺制程不断向3nm及以下演进,一个越来越清晰的趋势是:单纯依靠缩小晶体管尺寸来提升性能的传统路径,已不再像过去那样有效。在这一背景下,DTCO(设计-工艺协同优化)与STCO(系统-工艺协同优化)先后走上前台,成为延续芯片性能增长的关键方法论。 发展背景 过去几十年,半导体性能提升主要依赖“工艺驱动”:制程

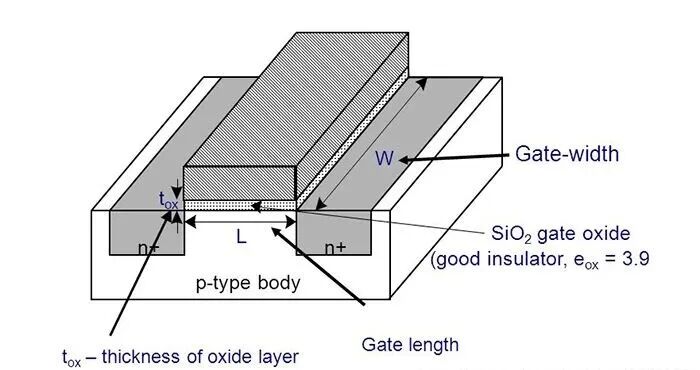

二氧化硅(SiO₂)和氮化硅(Si₃N₄)是最常用的两种介电材料, 本文将详细介绍氮化硅在不同温度区间的沉积方法。 介电材料作为绝缘层与光学薄膜,在半导体微芯片制造领域应用广泛。其中二氧化硅(SiO₂)和氮化硅(Si₃N₄)是最常用的两种介电材料,Si-SiO₂界面的优异特性,让该结构成为金属-氧化物-半导体场效应晶体管(MOSFET)的核心基石。本文将详细介绍Si₃N₄在不同温度区间的沉积方法。

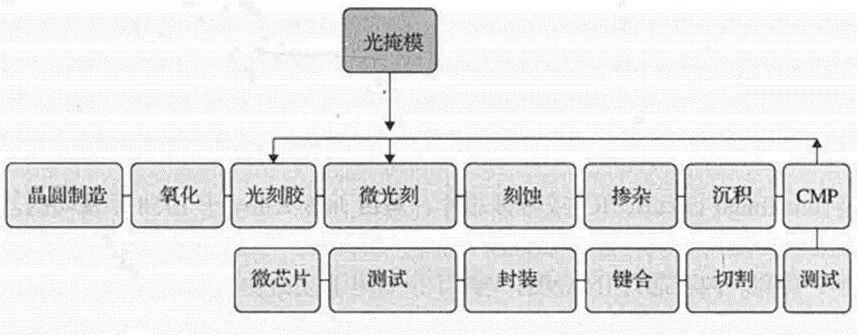

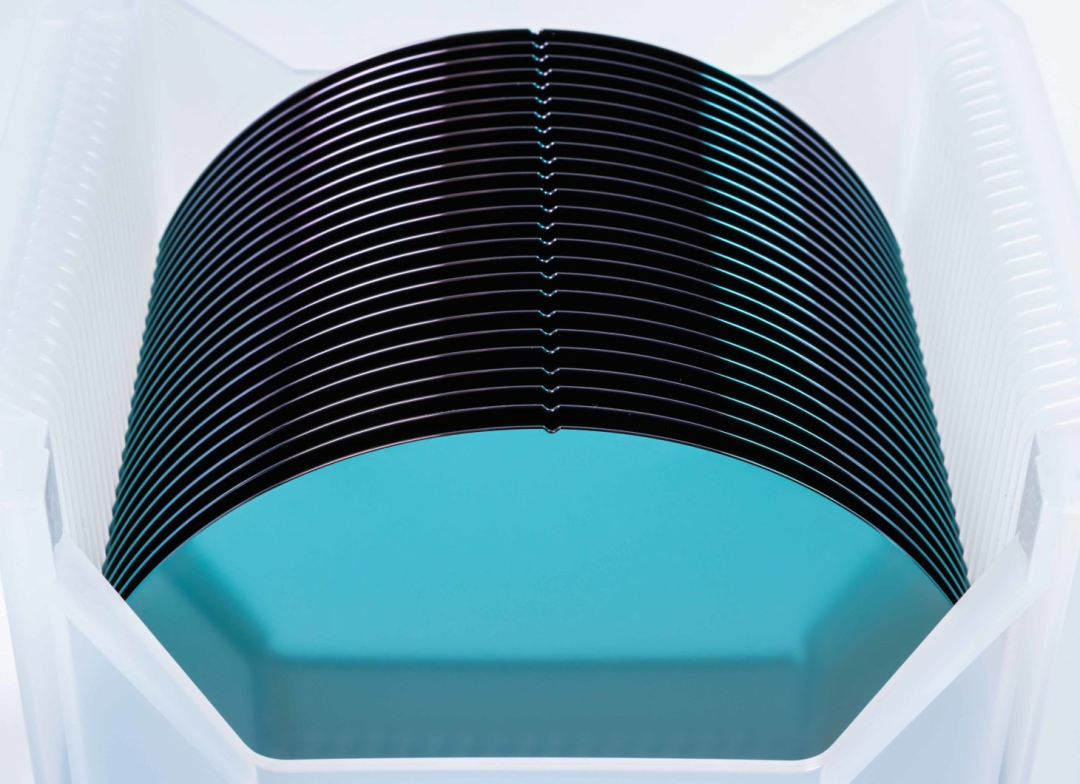

微芯片作为半导体产业的核心支柱, 本文将详细介绍微芯片的制造方法。 微芯片的制造方法 微芯片制造作为半导体产业的核心支柱,其工艺复杂性与技术精密性持续突破物理极限,正朝着3纳米以下制程、三维集成与绿色制造方向加速演进。 硅作为基础材料,凭借其独特的半导体特性——在栅极电压调控下实现导电与绝缘状态的切换,成为构建数亿晶体管开关阵列的理想载体,这一特性在集成电路中转化为二进制1/0的数字信号处理能力,

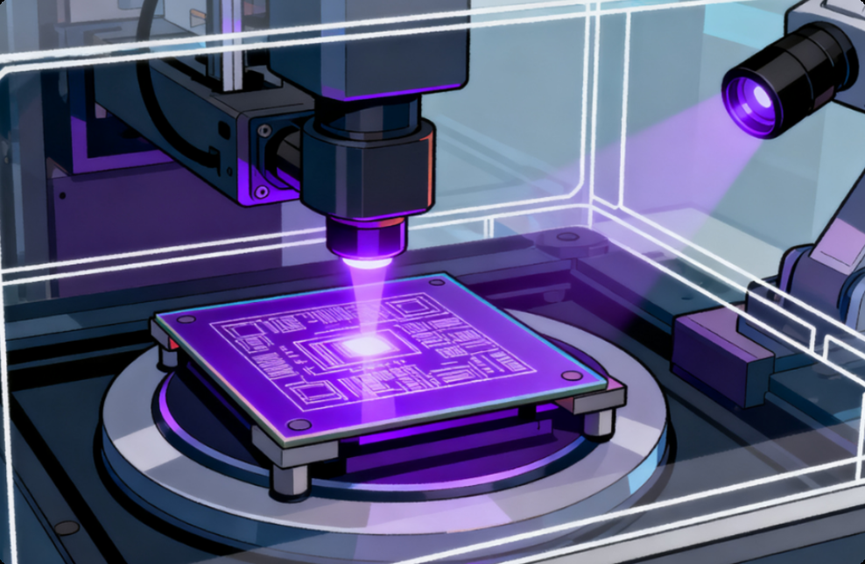

本文将详细介绍激光直写光刻技术。 激光直写光刻技术是一种利用曝光强度可控的激光束对光刻胶进行曝光,经显影后获得期望形貌三维微结构的无掩模光刻技术。该技术通过计算机对激光的曝光位置与强度进行数字化控制,实现对光刻胶的变剂量曝光,因此具有很高的制造灵活性。 与传统的投影光刻机相比,激光直写无需掩模板,甚至可直接用于生产掩模板。以激光为能量源的直写设备称为laser writer。从性价比看,激光直写适

4月23日消息,这可不是简单的二次拼接,而是从零开始的晶圆级手搓。 海外科技博主Dr.Semiconductor(半导体博士)完成了全球第一次DIY壮举。他在自家后院棚屋改造的洁净室里,成功制备出内存存储单元阵列,实现了史上首次在家自制RAM内存的突破。他还通过视频,完整展示了家用环境下芯片制造的全流程半导体工艺。 当下AI产业爆发,引发了全球内存市场的持续动荡。三星、美光、SK海力士三大

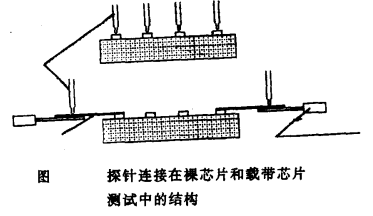

随着多芯片模块(MCM)复杂度的提升,已知好芯片(KGD)技术成为保障成品率的核心。单芯片合格率的微小差距将对模组良率产生指数级影响。本文深度解析KGD筛选的四大路径,对比压力接触与金属化连接等测试技术,并前瞻AI与3D封装驱动下的协同创新。 在半导体封装领域,已知好芯片(KGD)技术作为提升多芯片模块(MCM)成品率的核心支撑,其发展路径始终围绕“高合格率芯片筛选”与“高效缺陷检测”两大主线展开

芯片上的“2纳米”真的是指物理尺寸吗?从平面到FinFET,再到如今最前沿的GAA,制程节点已从实测刻度演变为性能勋章。本文带你拆解晶体管如何从二维“躺平”到三维“站立”,揭秘先进制程命名背后那些看不见的物理跨越与等效逻辑。 在芯片技术的宣传中,我们常常听到“5纳米”“3纳米”“2纳米”这样的词汇。很多人以为这指的是晶体管某个部分的实际物理尺寸,其实并不完全如此。从平面晶体管到FinFET,再到G

5G与硅光时代,高频损耗成为芯片设计的巨大挑战。高阻硅凭借极高的电阻率,成为阻断衬底损耗、消除寄生串扰的关键利器。本文带你深度解析HR-Si的技术内核,揭秘这一高性能射频前端与微波器件背后的“能量锁” 高阻硅(High-Resistivity Silicon,简称 HR-Si)是指具有极高电阻率的单晶硅材料。 普通逻辑芯片(如 CPU、GPU)所使用的标准硅片,为了导电和形成晶体管,通常会进行一

台积电在昨日举办的2026 北美技术论坛上,公布了其直至 2029 年的通用制程技术路线图。本次发布的核心亮点包括:名为 A12 与 A13 的 1.2nm、1.3nm 级制造工艺、对 N2 家族出人意料的延伸版本 N2U,以及截至 2029 年暂无计划在任何工艺节点使用高数值孔径极紫外光刻(**High-NA EUV**)。而本次技术公告中最值得关注的一点,或许是台积电正式确立了面向新一代工艺节

湿法腐蚀的侧蚀能“根治”吗?结论是:常规湿法侧蚀本质难除,但特定工艺下可控。若追求零侧蚀,则必须转向干法刻蚀。 一个干脆的结论:在绝大多数常规工艺中,湿法腐蚀的侧蚀(Undercut)无法完全消除,只能尽可能去控制和补偿。如果工艺要求绝对的“零侧蚀”(即完美的90度垂直侧壁),通常只能放弃湿法,改用干法刻蚀。 这主要是由湿法腐蚀的化学本质决定的。 为什么常规湿法生来带有侧蚀 常规的湿法腐蚀属于各

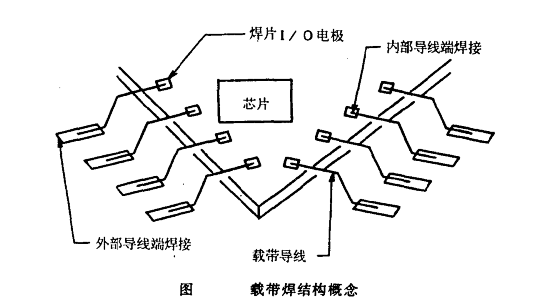

从传统到阵列,从ILB到OLB,载带焊如何在高密度互连的浪潮中突破性能与成本的“双刃”挑战,引领芯片封装技术的未来?本文为您深度解析。 载带芯片制造工艺及装连技术作为半导体封装领域的关键分支,其核心在于通过载带焊实现芯片与基板的高密度电气互连。 传统式载带焊通过芯片背面固定于基板,利用载带导线实现芯片I/O焊区与基板的电气连接,其优势在于工艺成熟、热传导性能优异,适用于大尺寸芯片及高功率应用场景

作为当前极紫外光刻技术的下一代演进,高数值孔径极紫外光刻(High-NA EUV)正从研发走向量产准备。它并非现有0.33 NA EUV的简单升级,而是通过将数值孔径提升至0.55,为2纳米以下逻辑节点和先进DRAM的关键层图形开辟新的工艺窗口。 技术原理与核心优势 High-NA EUV仍使用13.5nm波长的EUV光源,但将投影光学系统的数值孔径从0.33提高到0.55。根据瑞利准则,分辨率与

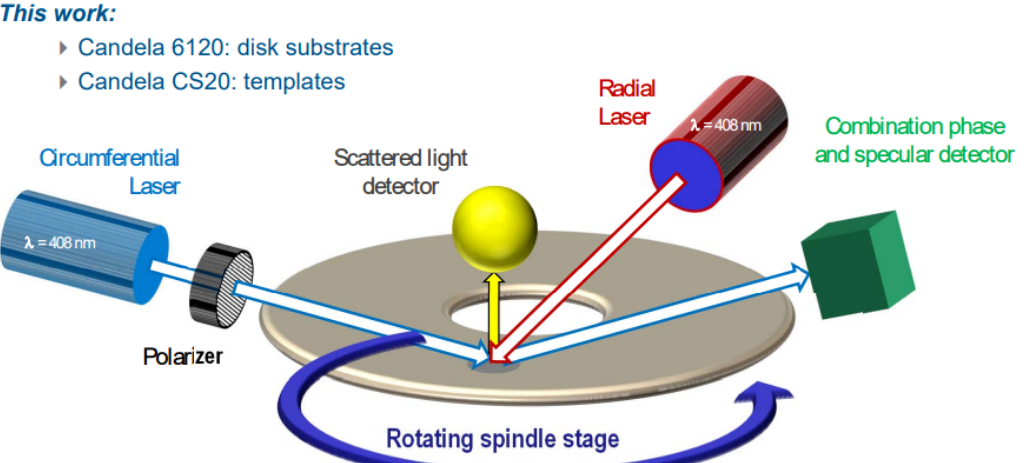

在追求极致性能与极小特征尺寸的集成电路制造领域,任何微小的异常均可能导致芯片失效。这些异常,即制造缺陷,是影响最终产品良率、性能与可靠性的直接因素。缺陷并非呈现单一形态,而是在晶圆经历上百道工艺步骤的过程中,不断演化、累积并显现,构成一幅复杂的图景。 一、缺陷分类 前端制程(Front End of Line, FEOL)是集成电路制造中形成晶体管等核心有源器件的阶段。在这一纳米尺度的精密制造过

氮化镓(GaN)性能优异,但客户最常问的是:它能像硅器件一样稳定工作十年以上吗? 作为全球功率半导体领导者,英飞凌的回答不仅是数据,更是一套贯穿设计、制造、认证与应用的全生命周期质量体系。在近日专题研讨中,英飞凌专家首次系统披露了CoolGaN™背后的可靠性工程。 质量之道:言出必行,零缺陷 英飞凌的质量理念是“言出必行”,承诺零缺陷。这背后是三大支柱: 设计可靠性:基于对氮化镓物理特性的深刻

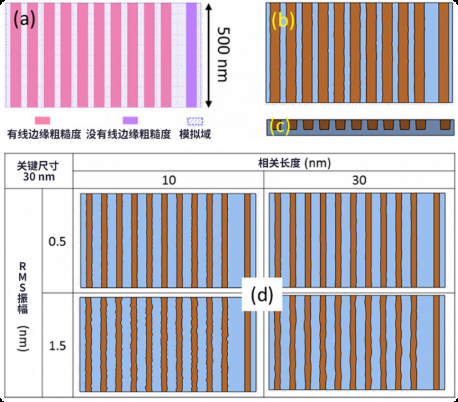

在纳米级光刻工艺中,线边缘粗糙度(Line Edge Roughness, LER)是指光刻图案边缘与理论上完美光滑边缘之间的随机偏差。显影后,光刻胶边缘在电子显微镜下呈现类似锯齿的不规则图形。与之相关的线宽粗糙度(LWR)则强调线宽沿长度方向的波动。随着特征尺寸持续缩小,LER并不会同比缩小,而工艺容差却不断收窄,这使得过去几纳米级的边缘起伏从“图形小瑕疵”转变为直接影响器件性能的关键因素。 L